# TOSHIBA

SERVICE TRAINING "Customer Satisfaction Through K nowledge"

TOSHIBA AMERICA CONSUMER PRODUCTS, INC. NATIONAL SERVICE DIVISION TRAINING DEPARTMENT 1420-B TOSHIBA DRIVE LEBANON, TENNESSEE 37087 PHONE: (615) 449-2360 FAX: (615) 444-7520

### FOREWORD

The material presented in this manual is provided for the technical training of TACP employees and qualified service personnel only.

The specific circuit reference designations, pin numbers, etc., are taken from the TP48E50/60 Service Manual, File Number 020-9508. The diagrams in this manual are simplified for training and should be used as a reference guide only when servicing the N5SS CTV Chassis. Refer to the applicable service data for detailed adjustment and servicing procedures.

#### NTDPJTV04

#### SERVICING TOSHIBA'S N5SS TELEVISION CHASSIS ©1996

#### TOSHIBA AMERICA CONSUMER PRODUCTS, INC.

National Service Division National Training Department 1420 Toshiba Drive Lebanon, TN 37087 (615) 449-2360

No part of this manual may be reproduced in whole or in part without prior written consent from Toshiba America Consumer Products, Inc., Service Division.

#### CONTENTS

#### **SECTION I OVERALL UNIT CHARACTERISTICS, BLOCK DIAGRAMS, LABS 1 & 2** 1. MAIN FEATURES ......1-2 2. MERITS OF BUS SYSTEM ...... 1-2 2-1. Improved Servciceability ......1-2 2-2. Reduction of Parts Count ......1-2 2-3. Quality Control ......1-2 3. COMPARISON/DIFFERENCES TG-1 ... 1-2 4. SPECIFICATIONS ......1-3 5. FRONT AND REAR CONTROL 5-1. Front View......1-4 5-2. Rear View ...... 1-5 5-3. Remote Control View ......1-6 6. '95 PJ-TV CHASSIS LAYOUT ...... 1-7 7. CONSTRUCTION OF CHASSIS ......1-8 9. AUDIO SIGNAL FLOW. ..... 1-11 10. POWER SUPPLY ......1-12 13. DIGITAL CONVERGENCE. ..... 1-15 14. LAB 1 ...... 1-16 15. LAB 2 ...... 1-20

#### **SECTION II**

#### **TUNER, IF/MTS/S.PRO MODULE**

| 1. | CIRCUIT BLOCK                         | 2-2 |

|----|---------------------------------------|-----|

|    | 1-1. Outline                          | 2-2 |

|    | 1-2. Major Features                   | 2-2 |

|    | 1-3. Audio Multiplex Demodulation     |     |

|    | Circuit                               | 2-3 |

|    | 1-4. A.PRO Section (Audio Processor). | 2-4 |

| 2. | PIP TUNER                             | 2-6 |

|    | 2-1. Outline                          | 2-6 |

|    |                                       |     |

#### **SECTION III**

#### CHANNEL SELECTION CIRCUIT

| 1. OUTLINE  | OF CHANNEL          |  |

|-------------|---------------------|--|

| SELECTIO    | ON CIRCUIT SYSTEM . |  |

| 2. OPERATIO | ON OF CHANNEL       |  |

| SELECTIO    | ON CIRCUIT          |  |

| 3. MICROCO  | OMPUTER             |  |

| 4. MICROCO  | OMPUTER TERMINAL    |  |

| FUNCTIO     | N                   |  |

| 5. EEPROM   | (QA02)              |  |

|             |                     |  |

- 7. SYSTEM BLOCK DIAGRAM ...... 3-7

- 8. LOCAL KEY DETECTION METHOD..3-8

- 9. ENTERING THE SERVICE MODE ...... 3-9

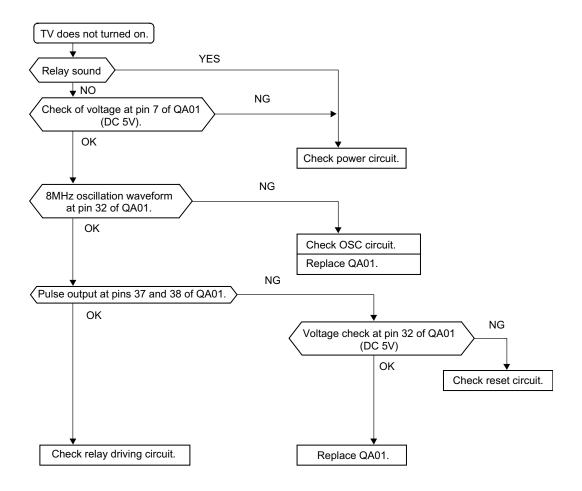

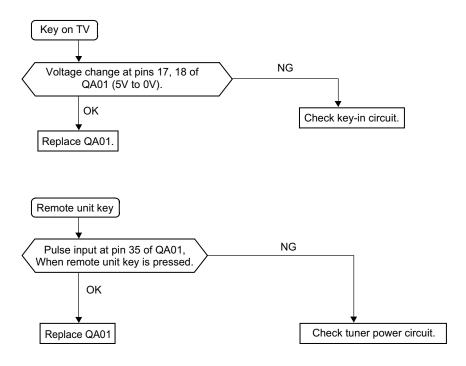

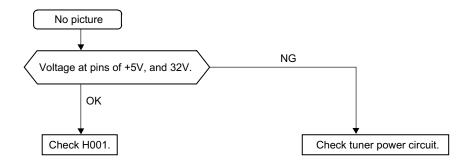

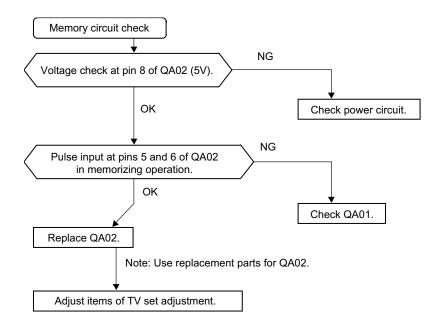

- 12. FAILURE DIAGNOSIS PROCEDURE 3-10

- 13. TROUBLE SHOOTING CHARTS ...... 3-13

#### **SECTION IV**

#### AUDIO OUTPUT CIRCUIT

#### **SECTION V**

#### **DSP CIRCUIT**

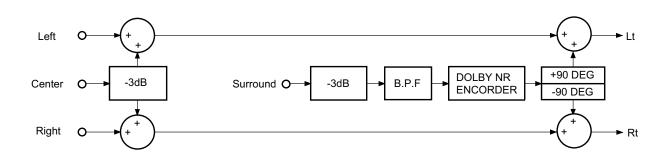

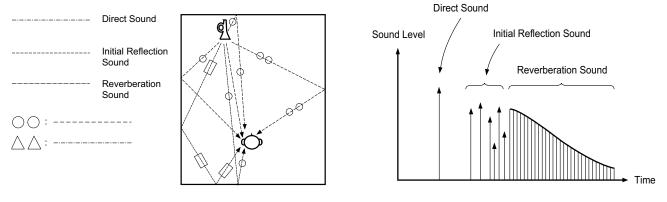

- 1. ORIGINS OF DOLBY SURROUND ...... 5-2

- 2. THE DOLBY MP MATRIX ...... 5-2

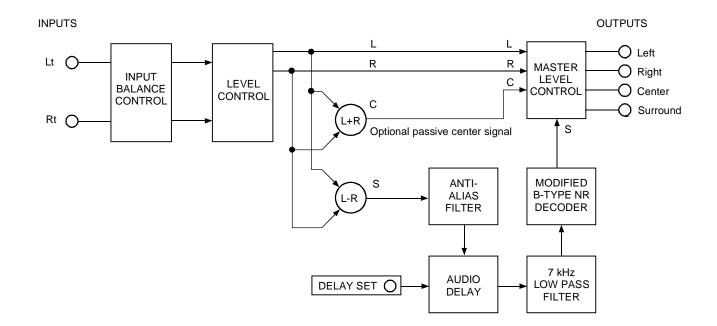

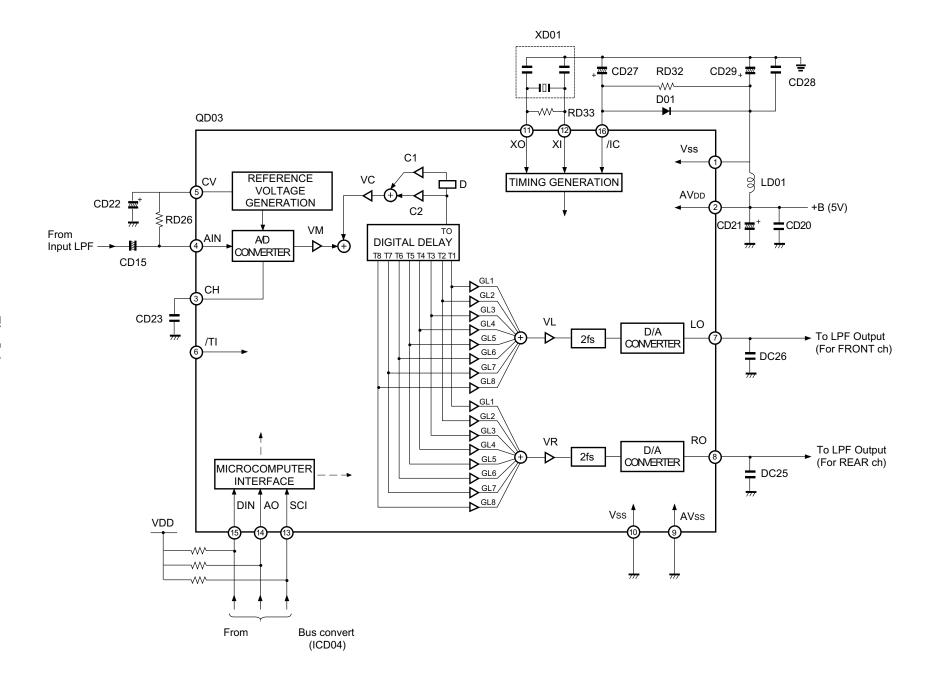

- 5. DSP (Digital Surround Processor) IC ..... 5-6

#### **SECTION VI**

#### **A/V SWITCHING CIRCUIT**

| 1. OUTLINE                  | 6-2 |

|-----------------------------|-----|

| 2. IN/OUT TERMINALS         | 6-2 |

| 3. CIRCUIT OPERATION        |     |

| 3-1. Composite Video Signal |     |

| 3-2. S-Video Signal         |     |

|                             |     |

#### **SECTION VII**

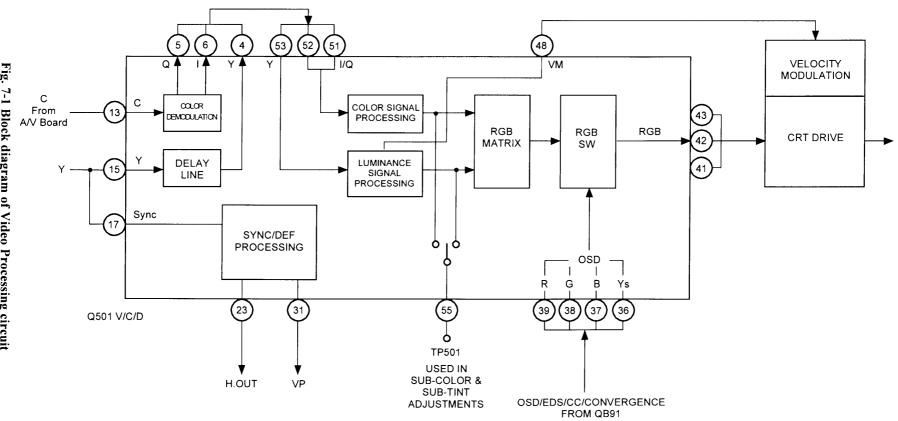

#### VIDEO PROCESSING CIRCUIT

- 3. CIRCUIT OPERATION ......7-2

#### **SECTION VIII**

#### V/C/D/IC

| 4. EMPLOYMENT OF CONTAINING      |

|----------------------------------|

| EACH FILTER (FOR S/H) INSIDE 8-2 |

5. LOW COST OF IC ......8-3

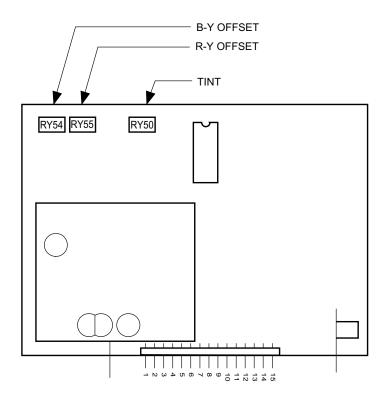

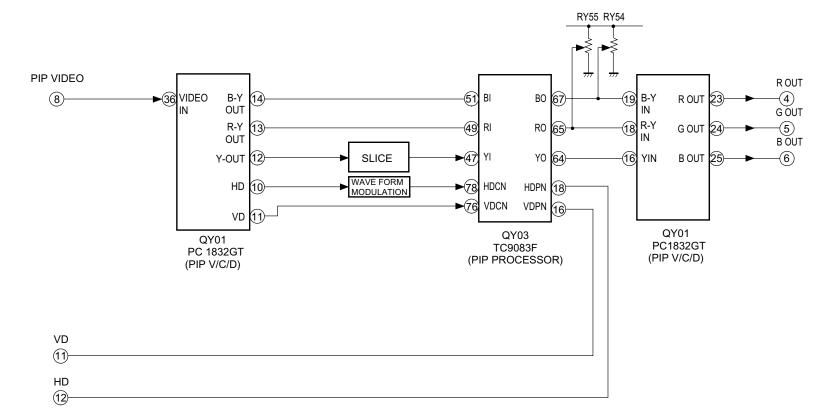

#### SECTION IX PIP MODULE

| PIP MODULE       |  |

|------------------|--|

| 1. BOARD LAYOUT  |  |

| 2. SIGNALS       |  |

| 3. BLOCK DIAGRAM |  |

#### **SECTION X**

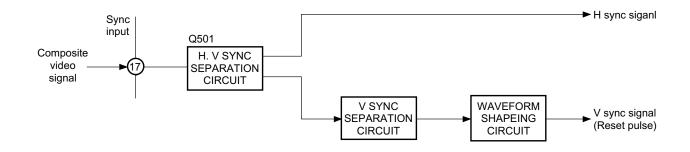

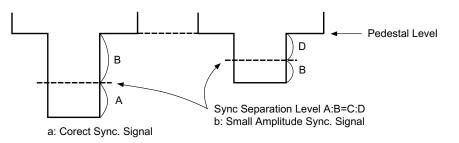

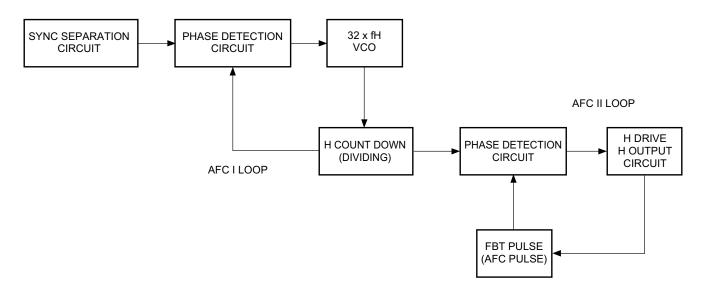

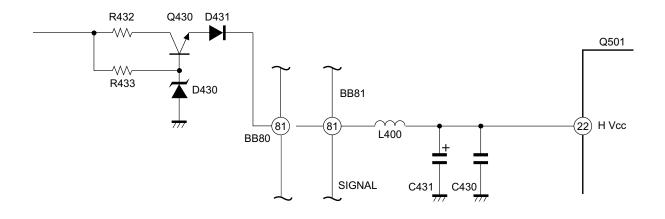

#### SYNC SEPARATION, H-AFC, H-OSCILLATOR CIRCUITS

| 1. | SYNC SEPARATION CIRCUIT             | 10-2 |

|----|-------------------------------------|------|

|    | 1-1. Theory of Operation            | 10-2 |

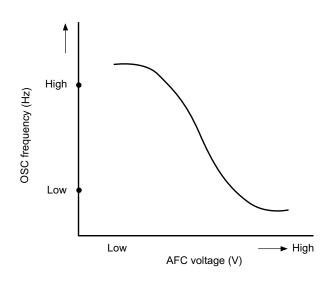

| 2. | H AFC (Automatic Frequency Control) |      |

|    | CIRCUIT                             | 10-3 |

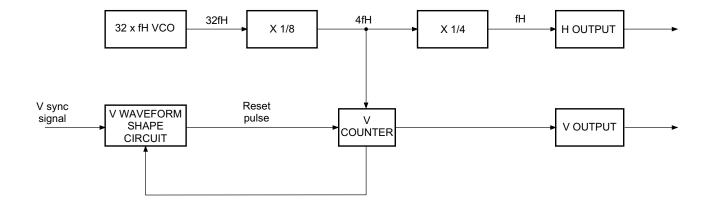

| 3. | H OSCILLATOR CIRCUIT                | 10-4 |

|    | 3-1. Outline                        | 10-4 |

|    | 3-2. Theory of Operation            | 10-4 |

|    |                                     |      |

#### SECTION XI

#### **VERTICAL OUTPUT CIRCUIT**

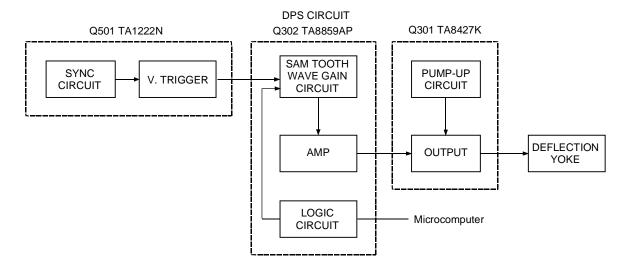

| 1. | OUTLINE                            | 11-2 |

|----|------------------------------------|------|

|    | 1-1. Theory of Operation           | 11-2 |

| 2. | V OUTPUT CIRCUIT                   | 11-3 |

|    | 2-1. Actual Circuit                | 11-3 |

|    | 2-2. Sawtooth Waveform Generation. | 11-3 |

|    | 2-3. V Output                      | 11-4 |

|    | 2-4. V Linearity Characteristic    |      |

|    | Correction                         | 11-6 |

| 3. | PROTECTION CIRCUIT FOR             |      |

|    | V DEFLECTION STOP                  | 11-7 |

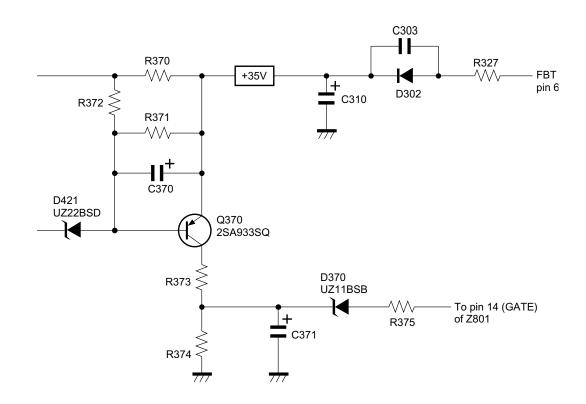

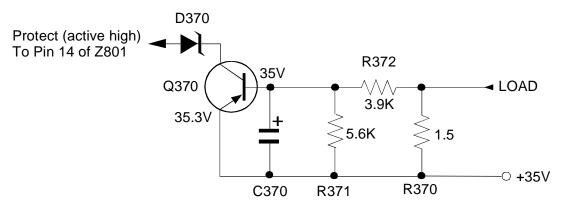

|    | 3-1. +35V Over Current             |      |

|    | Protection Circuit                 | 11-8 |

|    |                                    |      |

#### SECTION XII

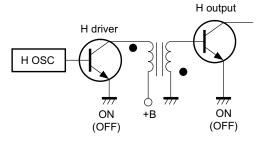

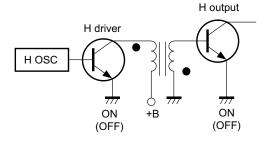

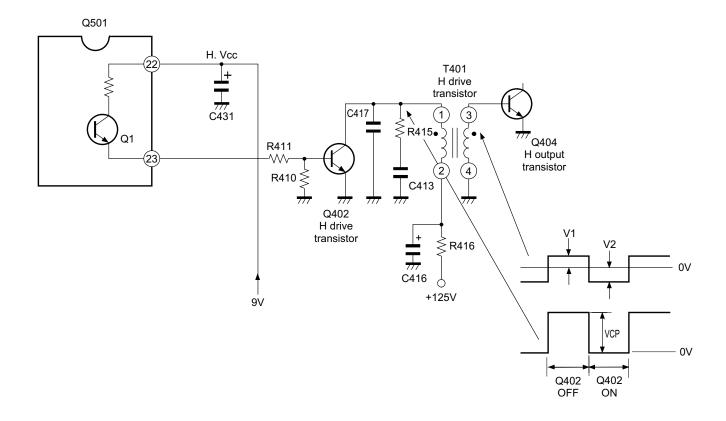

#### HORIZONTAL DEFLECTION CIRCUIT

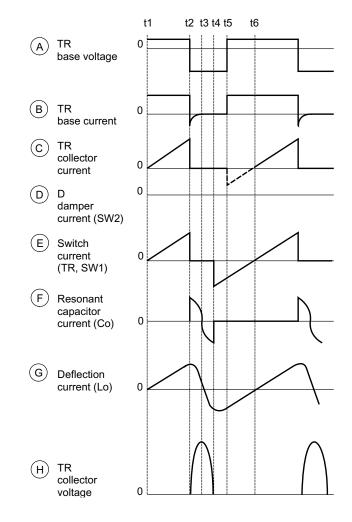

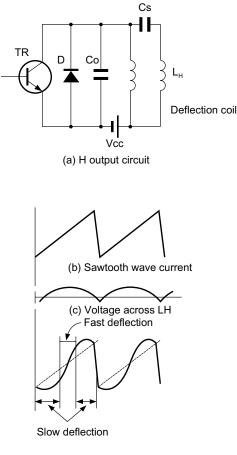

| 1. OUTLINE                       | 12-2    |

|----------------------------------|---------|

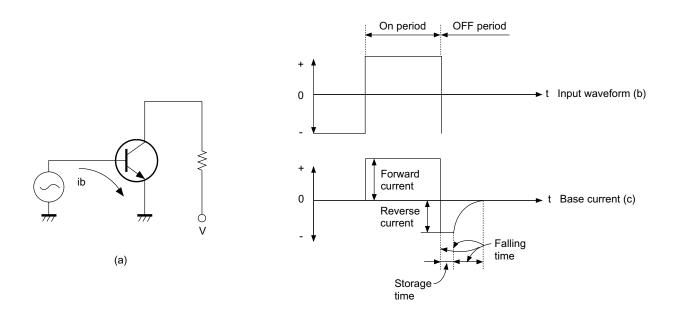

| 2. HORIZONTAL DRIVE CIRCUIT      | 12-2    |

| 2-1. Theory of Operation         | 12-2    |

| 3. BASIC OPERATION OF HORIZONT   | ΓAL     |

| DRIVE                            | 12-3    |

| 3-1. Theory of Operation         | 12-3    |

| 3-2. Drive System                | 12-4    |

| 3-3. Circuit Description         | 12-5    |

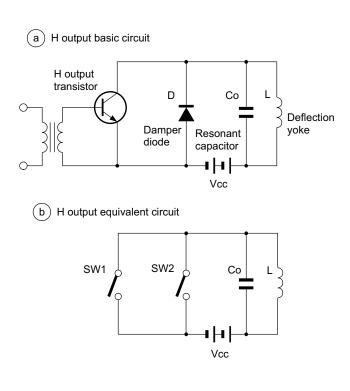

| 4. HORIZONTAL OUTPUT CIRCUIT .   | 12-6    |

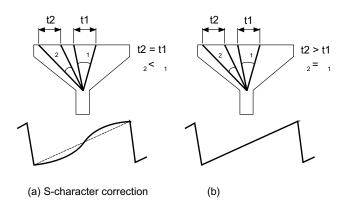

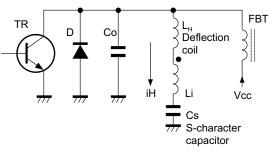

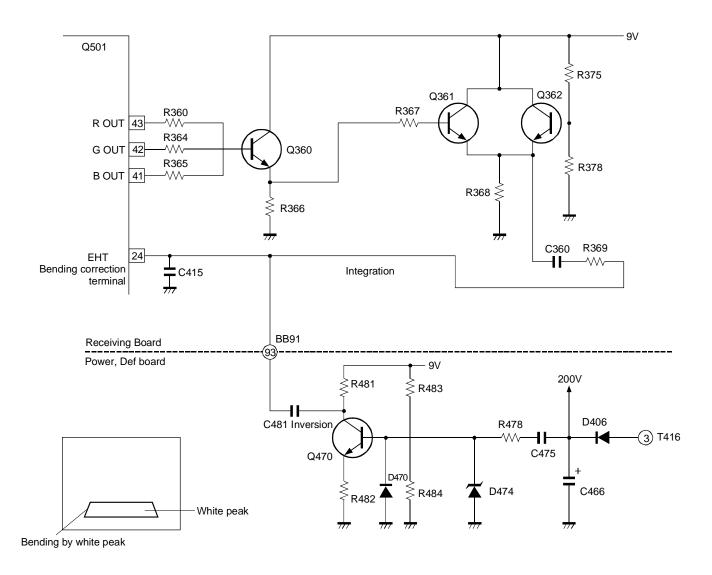

| 4-1. Theory of Operation         | 12-7    |

| 4-2. White Peak Bending          |         |

| Correction Circuit               | . 12-11 |

| 4-3. H Blanking                  | . 12-12 |

| 4-4. 200V Low Voltage Protection |         |

| -                                |         |

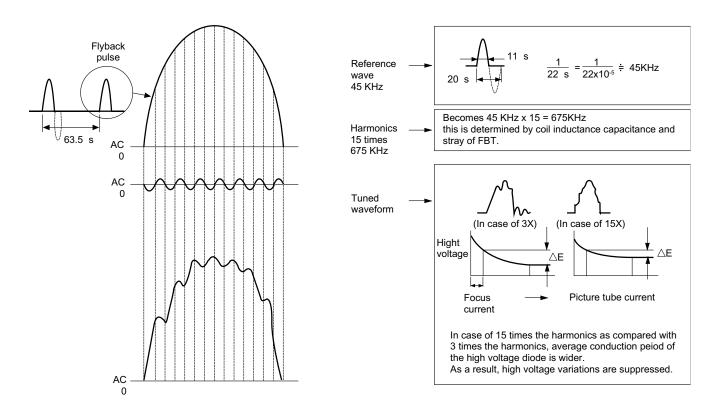

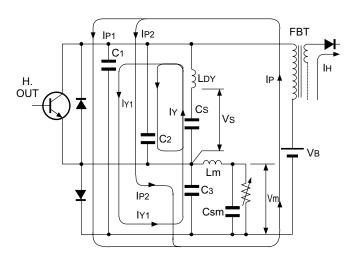

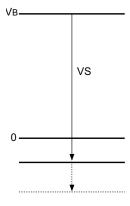

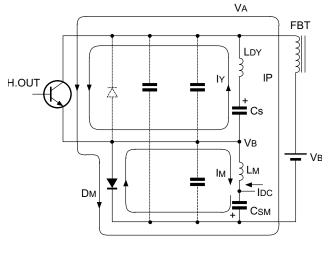

| 5. HIGH VOLTAGE GENERATION            |       |

|---------------------------------------|-------|

| CIRCUIT                               | 12-14 |

| 5-1. Theory of Operation              | 12-14 |

| 5-2. Operation Theory of the Harmonic | ;     |

| Non-Resonant System and Tuned         |       |

| Waveforms                             | 12-16 |

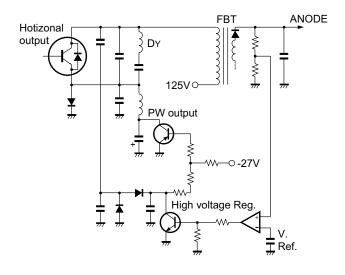

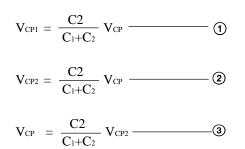

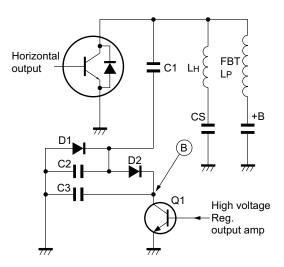

| 6. HIGH VOLTAGE CIRCUIT               | 12-17 |

| 6-1. High Voltage Regulator           | 12-17 |

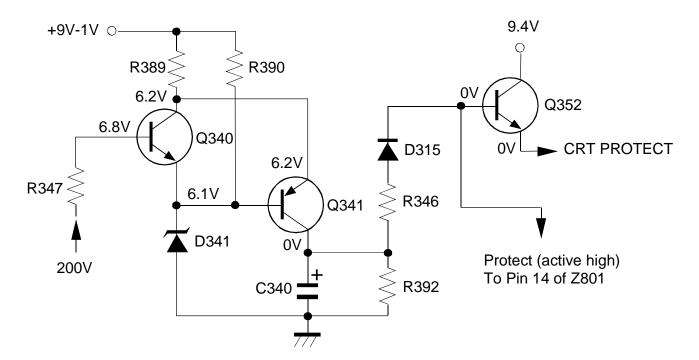

| 7. X-RAY PROTECTION CIRCUIT           | 12-20 |

| 7-1. Outline                          | 12-20 |

| 7-2. Operation                        | 12-20 |

| 8. OVER CURRENT PROTECTION            |       |

| CIRCUIT                               | 12-21 |

| 8-1. Outline                          | 12-21 |

| 8-2. Operation                        | 12-21 |

|                                       |       |

|                                       |       |

#### SECTION XIII

#### **DEFLECTION DISTORTION**

#### **CORRECTION CIRCUIT (DPC Circuit)**

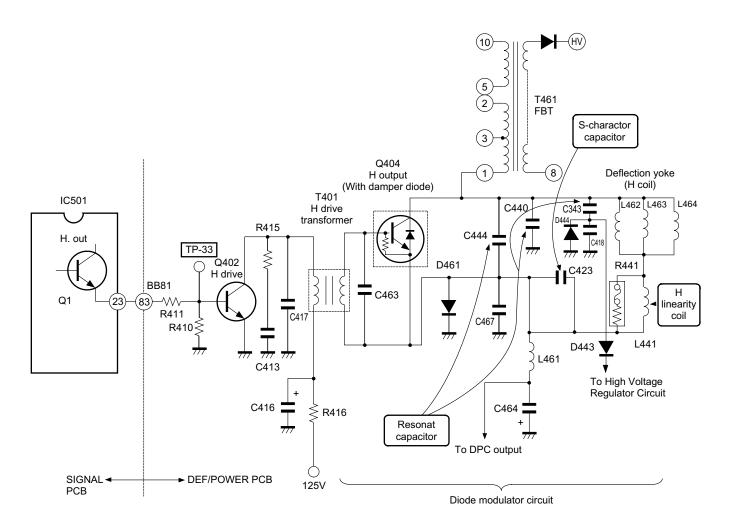

| 1. | DEFLECTION DISTORTION                 |      |

|----|---------------------------------------|------|

|    | CORRECTION IC (TA8859P)               | 13-2 |

|    | 1-1. Outline                          | 13-2 |

|    | 1-2. Functions and Features           | 13-2 |

|    | 1-3. Block Diagram                    | 13-2 |

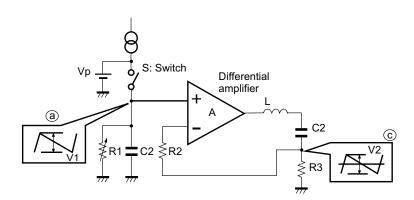

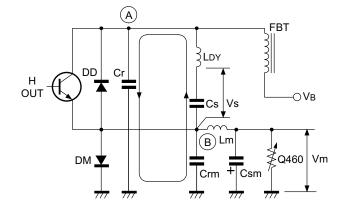

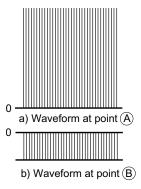

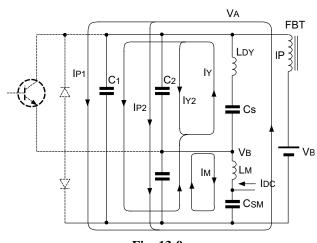

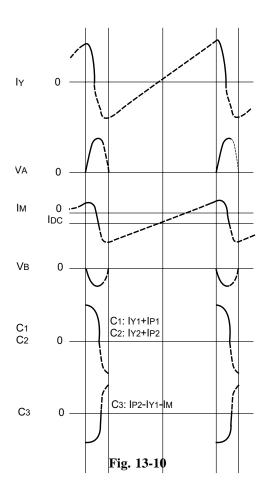

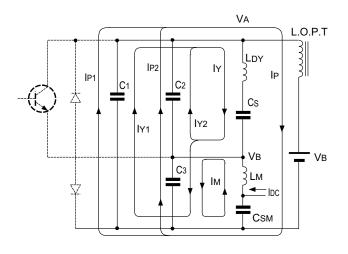

| 2. | DIODE MODULATOR CIRCUIT               | 13-3 |

| 3. | ACTUAL CIRCUIT                        | 13-4 |

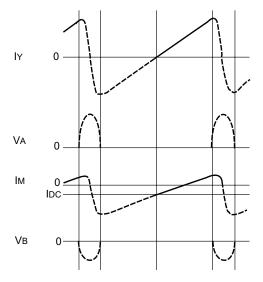

|    | 3-1. Basic Operation and Current Path | 13-5 |

|    |                                       |      |

#### SECTION XIV

#### **CLOSED CAPTION/EDS CIRCUIT**

| 1. | OUTLINE                  | 14 | -2 |

|----|--------------------------|----|----|

| 2. | DATA TRANSMISSION FORMAT | 14 | -2 |

| 3. | DISPLAY FORMAT           | 14 | -3 |

|    |                          |    |    |

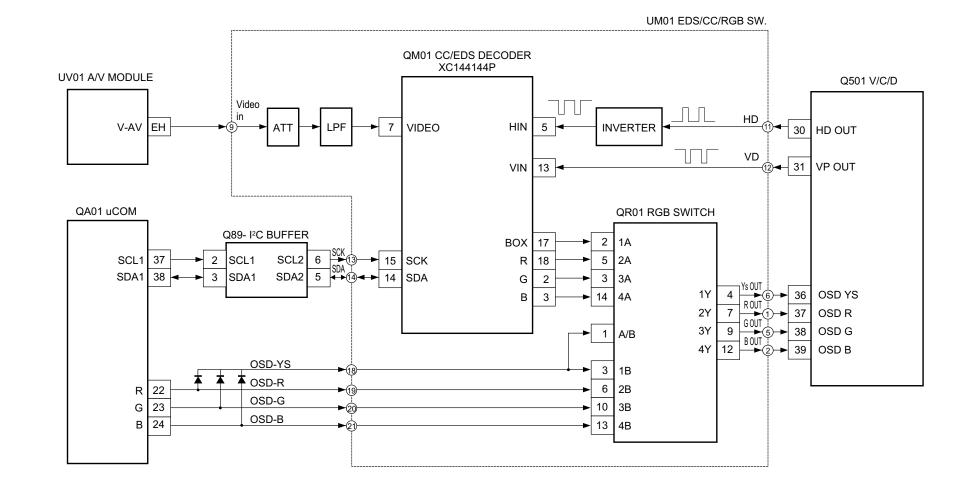

4. CIRCUIT OPERATION ......14-4

#### SECTION XV

#### DIGITAL CONVERGENCE CIRCUIT

| 1. | OUTLINE                                     | . 15-2 |

|----|---------------------------------------------|--------|

| 2. | CIRCUIT DESCRIPTION                         | . 15-2 |

|    | 2-1. Configuration                          | .15-2  |

|    | 2-2. Circuit Operation                      | .15-2  |

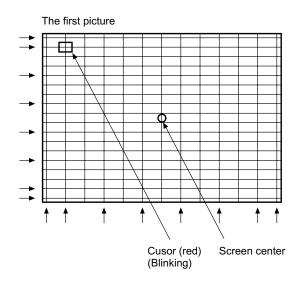

| 3. | PICTURE ADJUSTMENT                          | . 15-4 |

|    | 3-1. Change of Memory (E <sup>2</sup> PROM) | . 15-4 |

|    | 3-2. Service Mode                           | . 15-4 |

| 4. | ADJUSTING PICTURE                           |        |

|    | DIMENSION (Green picture)                   | . 15-6 |

| 5. | KEY FUNCTION OF REMOTE CONT                 | ROL    |

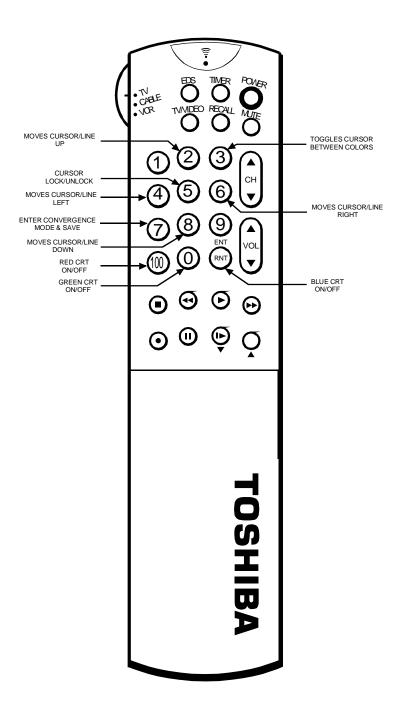

|    | UNIT                                        | . 15-7 |

| 6. | CONVERGENCE OUTPUT                          |        |

|    | CIRCUIT                                     | . 15-8 |

|    | 6-1. Outline                                | . 15-8 |

|    |                                             |        |

| 6-2. Circuit Description15-8   |

|--------------------------------|

| 7. CONVERGENCE TROUBLESHOOTING |

| CHART15-10                     |

| 8. LAB 3                       |

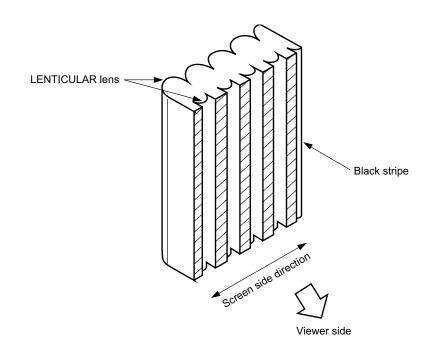

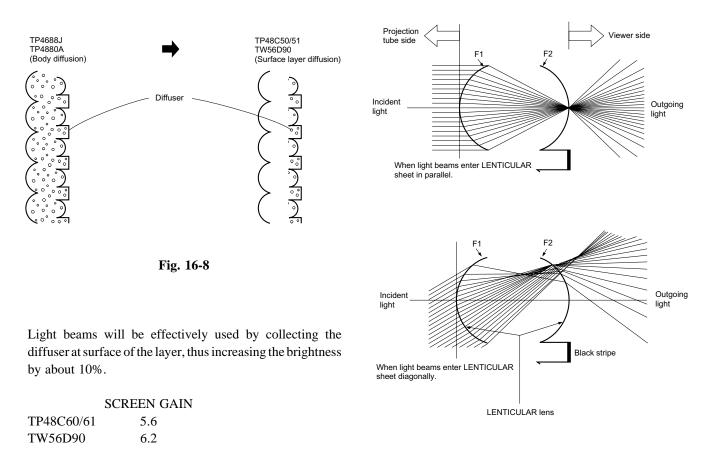

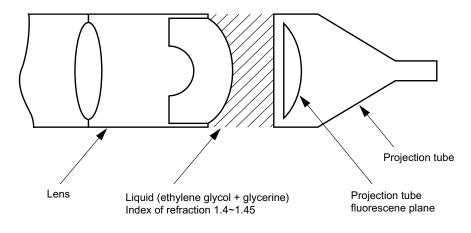

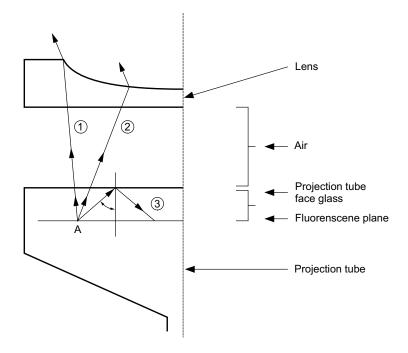

#### SECTION XVI OPTICAL SECTION

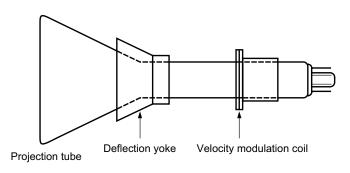

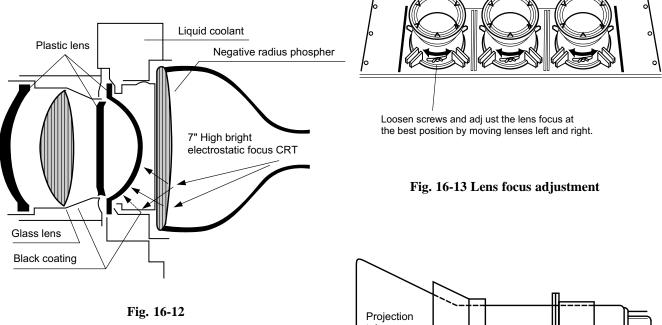

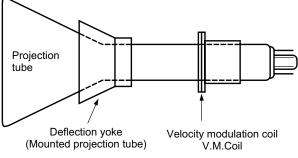

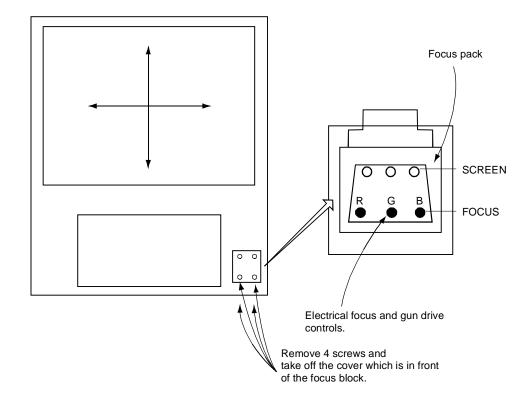

| 1. NECK COMPONENTS                | 16-2 |

|-----------------------------------|------|

| 1-1. Outline of Components Around |      |

| Neck of The Projection Tube       | 16-2 |

| 1-2. Theory of Operation          | 16-2 |

| 1-3. Projection Tube              | 16-3 |

| 2. FUNCTION OF KEY                |      |

| COMPONENTS                        | 16-4 |

| 2-1. Outline                      | 16-4 |

| 2-2. Theory of Operation          | 16-4 |

| 2-4. Optical Coupling Effect      |      |

| 2-5. Lens                         |      |

| 2-6. Focus Adjustment             |      |

|                                   |      |

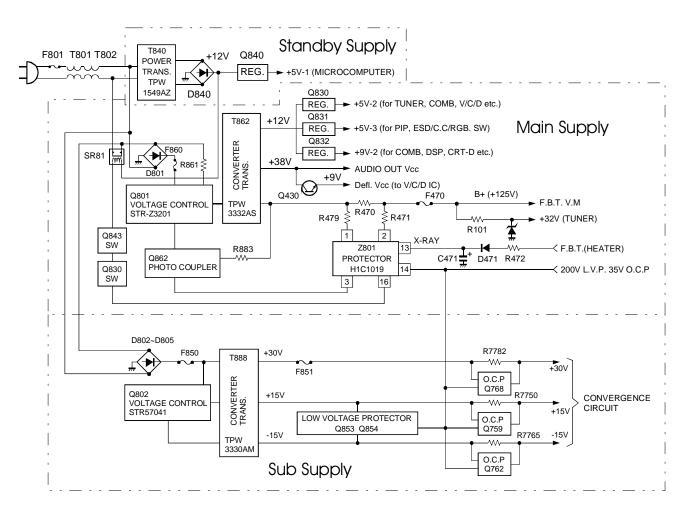

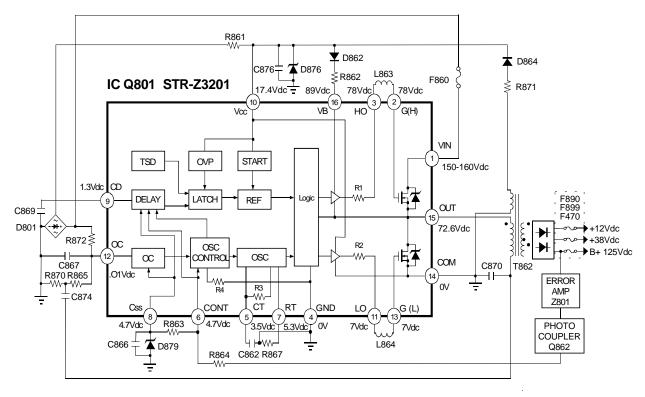

#### SECTION XVII POWER CIRCUIT

| 1  | OVEDVIEW     | ·               | 17 3 |

|----|--------------|-----------------|------|

| 1. | O V EK VIE W | ••••••••••••••• | 17-5 |

| 2. RECTIFYING CIRCUIT AND       |

|---------------------------------|

| STANDBY POWER SUPPLY 17-4       |

| 3. MAIN SUPPLY CIRCUIT 17-4     |

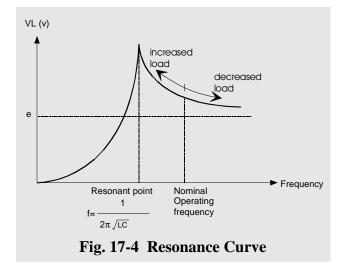

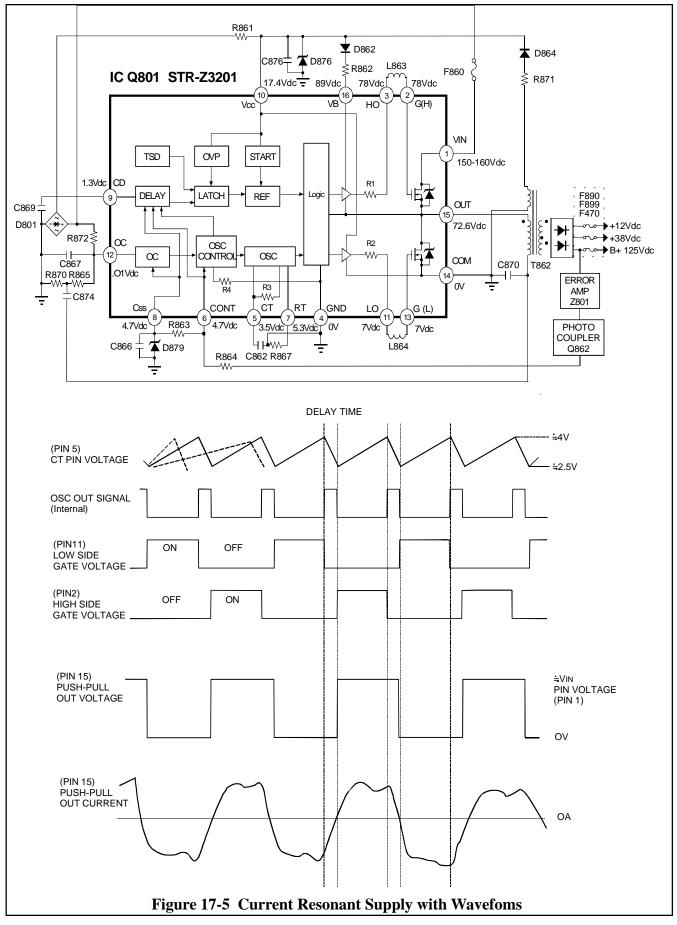

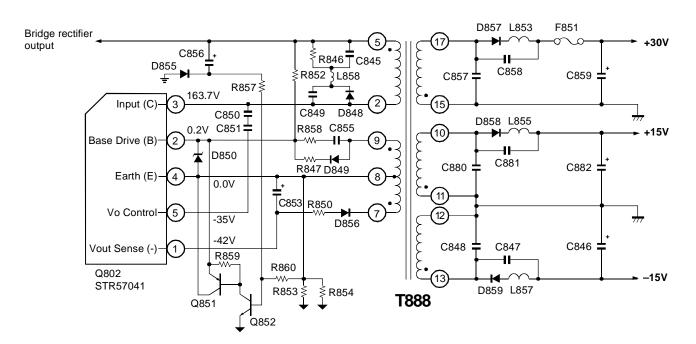

| 4. OUTLINE OF CURRENT RESONANT  |

| TYPE SUPPLY 17-4                |

| 5. FUNDAMENTAL THEORY 17-5      |

| 6. ACTUAL CIRCUIT 17-6          |

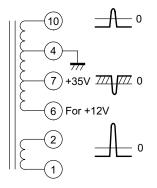

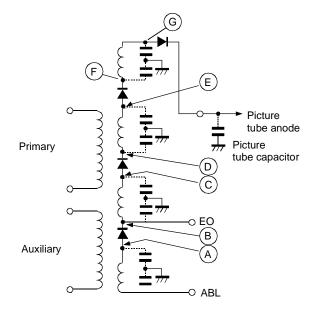

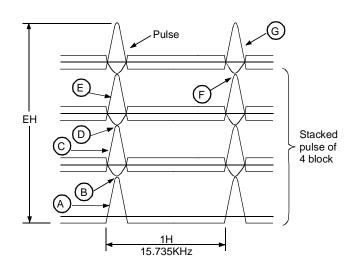

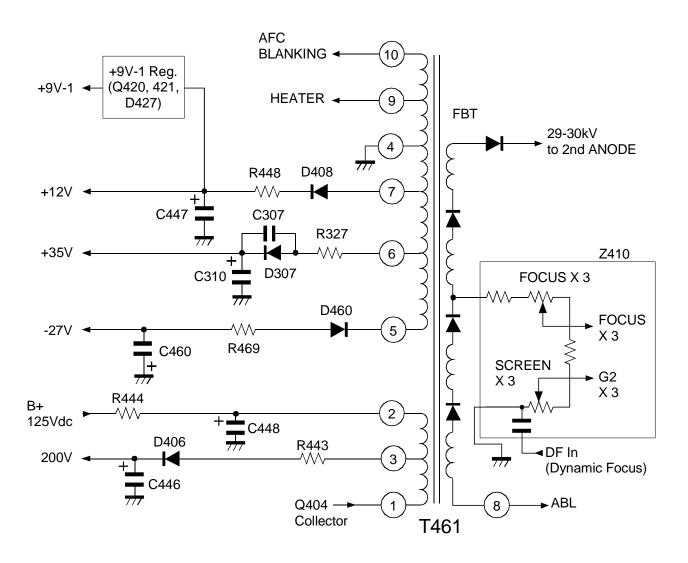

| 7. SCAN DERIVED VOLTAGES 17-8   |

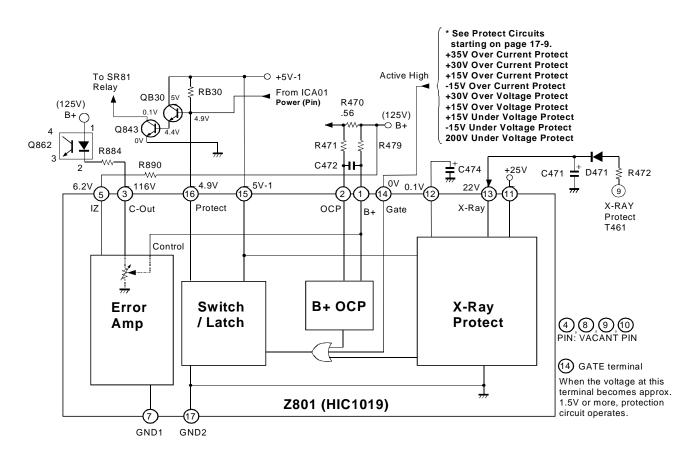

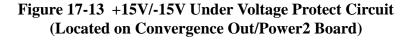

| 8. PROTECTOR MODULE (Z801) 17-9 |

| 9. SUB POWER SUPPLY17-10        |

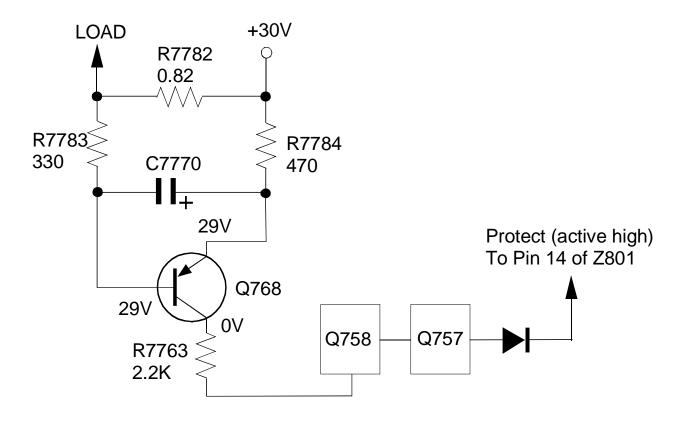

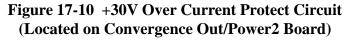

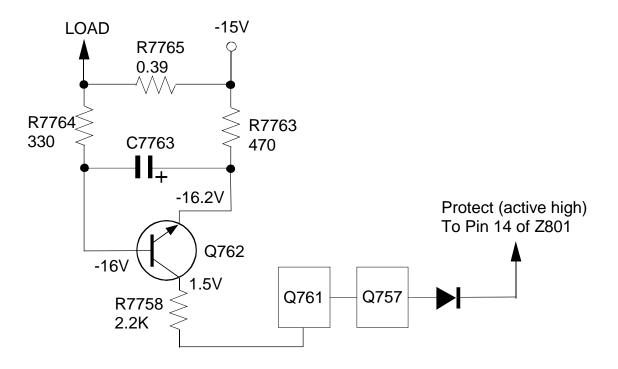

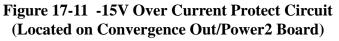

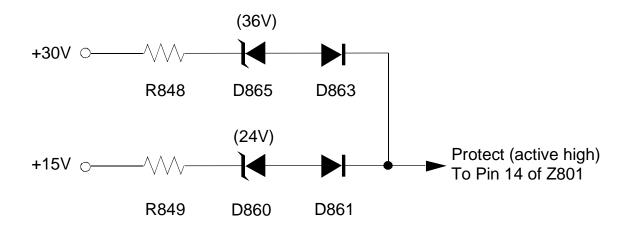

| 10. PROTECT CIRCUITS 17-11      |

| 11. LAB 4 17-15                 |

|                                 |

|                                 |

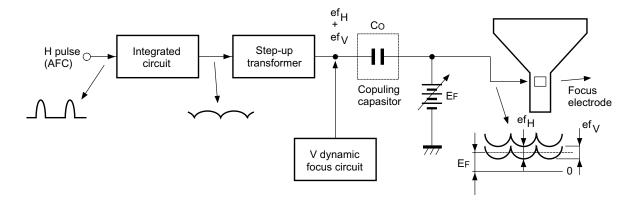

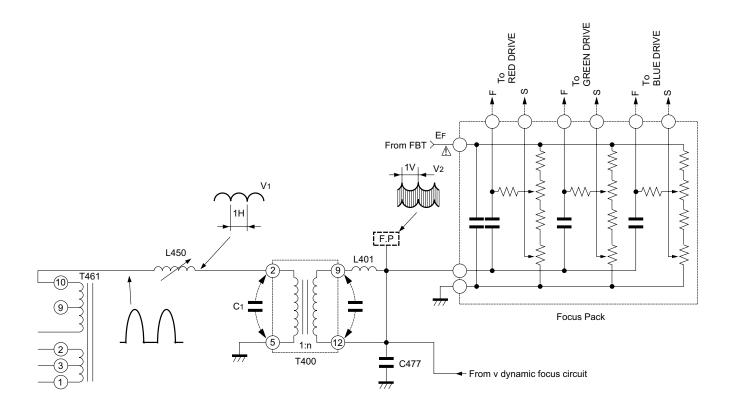

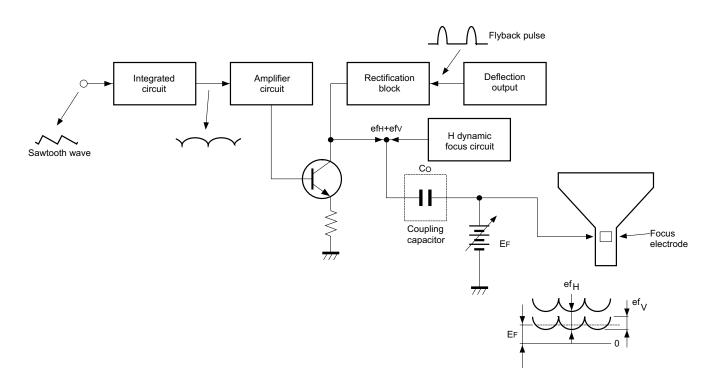

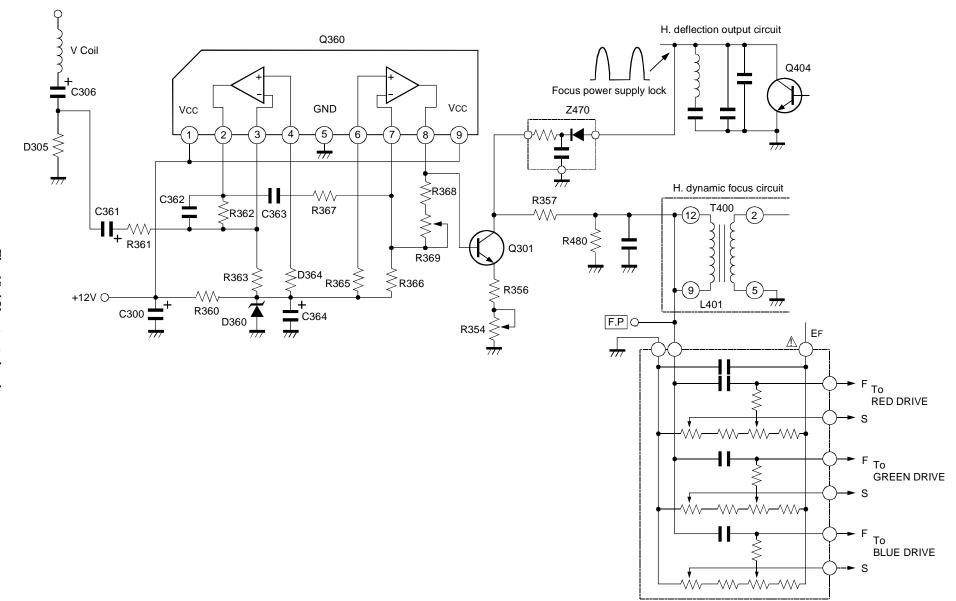

#### SECTION XVIII DYNAMIC FOCUS CIRCUIT

| 1. | OUTLINE                   | 8-2 |

|----|---------------------------|-----|

|    | H DYNAMIC FOCUS CIRCUIT1  |     |

|    | 2-1. Theory of Operation1 |     |

|    | 2-2. Circuit Operation1   |     |

| 3. | V DYNAMIC FOCUS CIRCUIT1  |     |

|    | 3-1. Theory of Operation1 | 8-4 |

|    | 3-2. Circuit Operation1   | 8-5 |

|    | -                         |     |

## SECTION I OVERALL UNIT CHARACTERISTICS BLOCK DIAGRAMS LABS 1 & 2

### **SECTION I**

## **OVERALL UNIT CHARACTERISTICS**

#### **1. MAIN FEATURES**

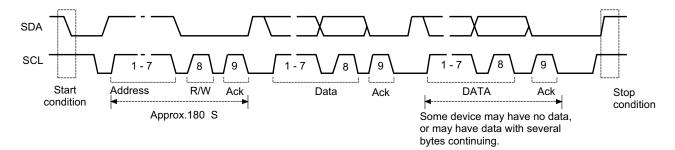

The main feature of Toshiba's projection television model TP48E60, is the use of the N5SS (TG-1C) chassis. This chassis utilizes a bus control system, developed by PHILIPS Corporation, called the I<sup>2</sup>C (or IIC) bus. IIC stands for Inter-Integrated Circuit control. This bus co-ordinates the transfer of data and control between ICs inside the Television. It is a bi-directional serial bus consisting of two lines, namely SDA (Serial DATA), and SCL (Serial CLOCK).

Digital data which is passed along the bus is received by individual devices and can be either command or data. Digital-to analog converters are also found within some of the ICs, allowing them to be addressed and controlled by strings of digital instructions, replacing those functions which were previously implemented by external potentiometers.

#### 2. MERITS OF THE BUS SYSTEM

#### 2-1. Improved Serviceability

Most of the adjustments previously made by resetting variable resistors and/or capacitors can be made on the new chassis by operating the remote control and seeing the results on the television screen. This allows adjustments to be made without removing covers on the unit thus increasing servicing speed and efficiency.

#### 2-2. Reduction of Parts Count

The use of digital-to-analog converters built into the ICs, allowing them to be controlled by software, has eliminated or reduced the requirement for many discrete parts such as potentiometers and trimmers, etc.

#### 2-3. Quality Control

The central control of adjustment data makes it easier to understand, analyze, and review the data, thus improving the quality of the product.

#### 3. COMPARISON/DIFFERENCES OF TG-1 CHASSIS

Toshiba's concept for the TG-1 chassis was to create a sort of universal chassis which, with minimal changes, could be used as a standard throughout the entire Toshiba color television lineup starting in 1995. TG-1 stands for "Toshiba Global 1". The TG-1 chassis can be found in several different models and varies in both complexity and features.

| Root    | TG-1     | Typical    | Picture and |

|---------|----------|------------|-------------|

| Chassis | Chassis  | Sizes      | Features    |

| N5E     | A1       | 13, 19     | Less        |

| N5ES    | A2       | 20, 32     |             |

| N5S     | A2 - LEM | 20, 32     |             |

| N5S     | В        | 27, 32     |             |

| N5SS    | С        | 27 thru 35 | More        |

| Typical Chass | is Examples |

|---------------|-------------|

| Model         | TG-1        |

| CF13E22,23    | A1          |

| CF19E22       | A1          |

| CF20E30       | A1          |

| CF20E40       | A1          |

| CN27E55       | A2          |

| CF30E50       | A2          |

| CF32E50       | A2          |

| CF32E55       | A2          |

| CX32E60       | В           |

| CX32E60       | В           |

| CN27E90       | С           |

| CX32E70       | С           |

| CN32E90       | С           |

| CN35E15       | С           |

| TP48E50,51    | С           |

| TP48E60,61    | C           |

| TP55E50,51    | Ċ           |

| TP55E80.81    |             |

| TP61E80       | C           |

| TP48E90       | С           |

#### 4. SPECIFICATIONS

|                                      | CHASSIS                                                                                                                                                                                                                                                                                                                | С                                                                                        | С                                                                                        | С                                         | С                                                                                       | С                                              | С                                                         |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------|

|                                      | MODEL Nbr                                                                                                                                                                                                                                                                                                              | TP48E50                                                                                  | TP48E60                                                                                  | TP48E90                                   | TP55E50                                                                                 | TP55E80                                        | TP61E80                                                   |

| SPEC                                 | CIFICATION                                                                                                                                                                                                                                                                                                             | TP48E51                                                                                  | TP48E61                                                                                  |                                           | TP55E51                                                                                 | TP55E81                                        | STEP-UP                                                   |

| *<br>E<br>N<br>E<br>R<br>A           | <ol> <li>Picture Size#</li> <li>Channel Capacity</li> <li>C. Caption</li> <li>MTS with dbx</li> <li>Bass, Tre/Balance</li> <li>Sub-Audio-Program</li> <li>Remote Control</li> </ol>                                                                                                                                    | 48"-D/S<br>181ch<br>•<br>•<br>*A-Uni (42k                                                | 48"-D/S<br>181ch<br>•<br>•<br>•<br>A-Uni (42k                                            | 48"-D/S<br>181ch<br>•<br>•<br>*Intelig+EZ | 55"-D/S<br>181ch<br>•<br>•<br>•<br>A-Univ (42k                                          | 55"-D/S<br>181ch<br>•<br>•<br>•<br>A-Univ (43k | 61"-D/S<br>181ch<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  |

| L                                    | 8 Picture-in-Picture<br>9 LED Indicator (RED)<br>10 Local Key                                                                                                                                                                                                                                                          | * ● (1TN)<br>● (P)<br>8key                                                               | ● (2TN)<br>● (P)<br>8key                                                                 | ● (2TN)<br>● (P)<br>8key                  | ● (1TN)<br>● (P)<br>8key                                                                | ● (2TN)<br>● (P)<br>8key                       | ● (2TN)<br>● (P)<br>8key                                  |

| *<br>S<br>O<br>U                     | <ol> <li>Dolby Surround</li> <li>Dig-Sound Processor</li> <li>Front Surround</li> <li>Cyclone ABX</li> <li>Sub-Bass-System</li> </ol>                                                                                                                                                                                  |                                                                                          |                                                                                          | ●(Prolo)<br>● (DSP4ch)<br>—<br>●          |                                                                                         | • (DSP4ch)<br><br>•                            | • (DSP4ch)<br><br>•                                       |

| N<br>D                               | 16 Audio Output<br>17 Speaker Size & Nbr                                                                                                                                                                                                                                                                               | 14Wx2<br>160Rx2                                                                          | 14Wx2                                                                                    | 14Wx2, 10Wx2<br>& 10Wx2<br>160Rx2         | 14Wx2<br>160Rx2                                                                         | 14Wx2<br>& 10Wx2<br>160Rx2                     | 14Wx2<br>& 10Wx2<br>160Rx2                                |

| *<br>P<br>I<br>C<br>T<br>U<br>R<br>E | <ul> <li>18 Comb Filter</li> <li>19 Dynamic Focus #</li> <li>20 Scan Velocity Modu</li> <li>21 Vert Contour Corre</li> <li>22 Black Level Expand</li> <li>23 Flesh Tone Correct</li> <li>24 Dynamic Noise Reduc</li> <li>25 Picture Preference</li> <li>26 Digital-Convergence</li> <li>27 Horiz Resolution</li> </ul> | ● (DIG)<br>● (RGB)<br>—<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>● | ● (DIG)<br>● (RGB)<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>● | & REAR SPK                                | ● (DIG)<br>● (RGB)<br><br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>● | & REAR SPK                                     | & REAR SPK<br>(3D-Y/C)<br>(RGB)<br><br>0<br>0<br>0<br>800 |

| *<br>O<br>T<br>H<br>E<br>R           | <ul> <li>28 Parental-Ch Lock</li> <li>29 Channel Label (32ch)</li> <li>30 3-Language Display</li> <li>31 Clock/Off-Timer</li> <li>32 Favorite Channel</li> <li>33 Extended-Data-Servi</li> <li>34 Star-Sight-Decoder</li> </ul>                                                                                        | •<br>•<br>• / •                                                                          | •<br>•<br>• / •                                                                          | •<br>•<br>• / •                           | •<br>•<br>• / •                                                                         | •<br>•<br>• / •                                | •<br>•<br>•<br>•<br>•                                     |

| *<br>E<br>R<br>M<br>S                | <ul> <li>35 S-Video In-Term</li> <li>36 Audio, Video-In/Out</li> <li>37 Front AV Jack</li> <li>38 Variable Audio Out</li> <li>39 2-RF Input</li> <li>40 Ext Speaker Term</li> <li>41 PIP Audio Out Jack</li> <li>42 Center-Ch-Aud-Input</li> </ul>                                                                     | • (1+1)<br>1+2/1<br>•<br>*<br>•<br>                                                      | • (1+1)<br>1+2/1<br>•<br>•<br>•                                                          | • (1+1)<br>1+2/1<br>•<br>•                | • (1+1)<br>1+2/1<br>•<br>•<br>•<br>•                                                    | • (1+1)<br>1+2/1<br>•<br>•<br>•<br>•           | ● (1+1)<br>1+2/1<br>●<br>●<br>●                           |

| AC                                   | 43 Speaker-Box<br>*Cabinet                                                                                                                                                                                                                                                                                             |                                                                                          | <br>NEW                                                                                  | • (SS-SR94<br>NEW                         |                                                                                         | • (SS-SR94<br>NEW                              | • (SS-SR94<br>NEW                                         |

|                                      | PARTS SUPPLY (ISO)                                                                                                                                                                                                                                                                                                     |                                                                                          |                                                                                          |                                           |                                                                                         |                                                |                                                           |

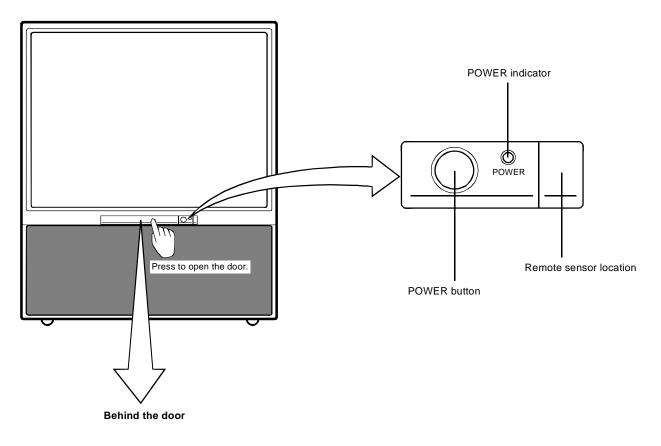

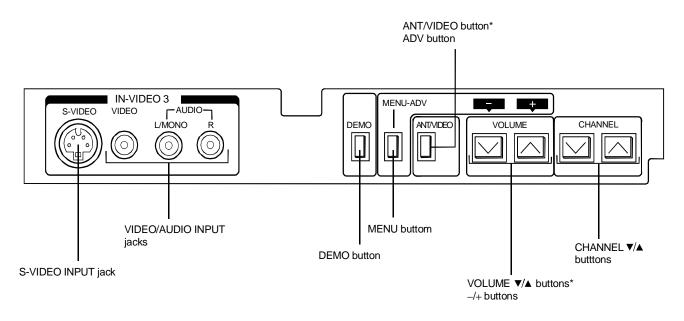

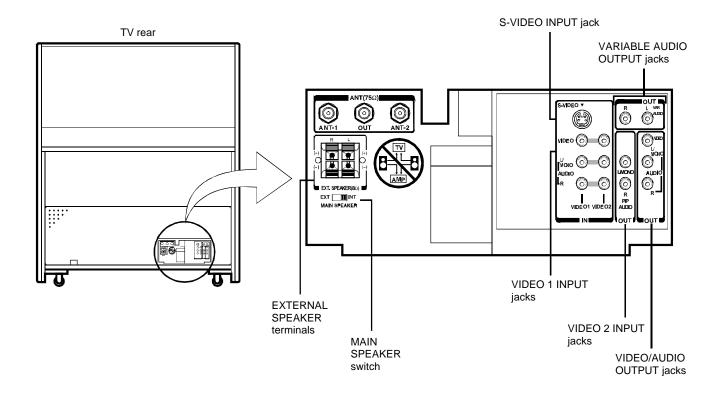

#### 5. FRONT AND REAR CONTROL VIEWS

#### 5-1. Front View

Fig. 1-1

\* These buttons have dual functions.

Fig. 1-3

Fig. 1-4

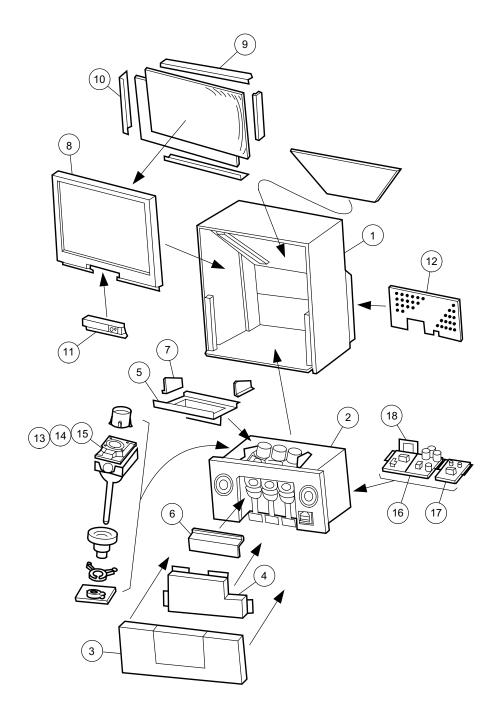

#### 7. CONSTRUCTION OF CHASSIS

- (1) WOOD CABINET

- (2) LIGHT BOX

- 3 SPEAKER GRILLE

- (4) FRONT COVER

- 5 CRT MOUNTING

- (6) SHIELD FRONT

- (7) SHIELD SIDE

- (8) SCREEN BEZEL

- (9) SCREEN BRACKET L

- (10) SCREEN BRACKET S

- (11) CONTROL PANEL

- (12) BACK BOARD

- (13) COUPLING R

- (14) COUPLING G

- (15) COUPLING B

- (16) CHASSIS FRAME MAIN

- (17) CHASSIS FRAME POWER

- (18) AV TERMINAL BOARD

Fig. 1-6

#### 8. VIDEO SIGNAL FLOW BLOCK DIAGRAM

#### **Basic Circuit Operation**

The basic operation of the TG-1 chassis is illustrated in the block diagrams, figures 1-7 through 1-12. Although these diagrams focus on the TP48E60, the video and audio signal flow diagrams can be applied to any TG-1 chassis with minor modifications.

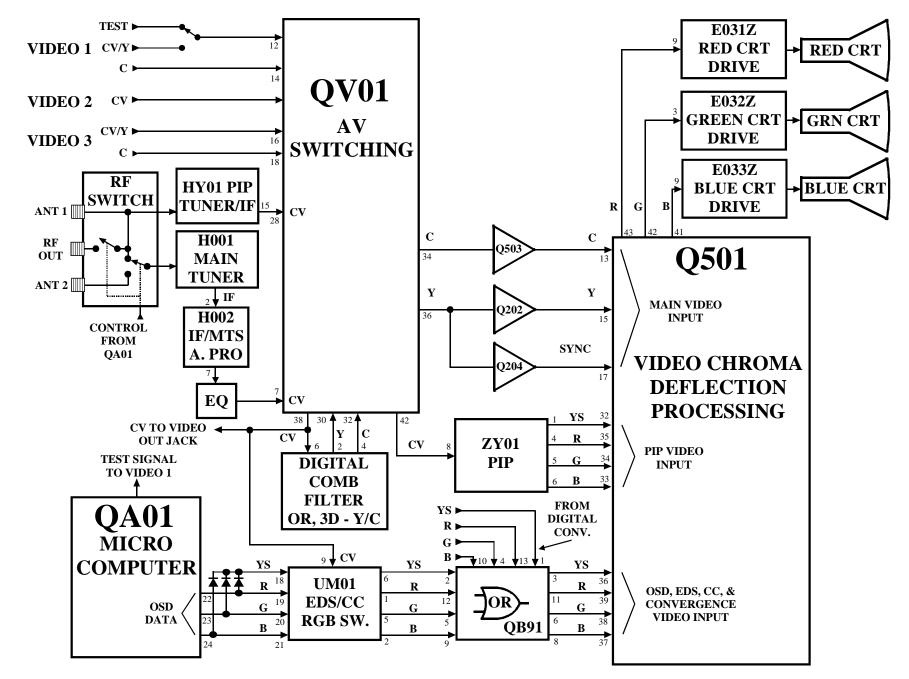

#### Video Signal Flow

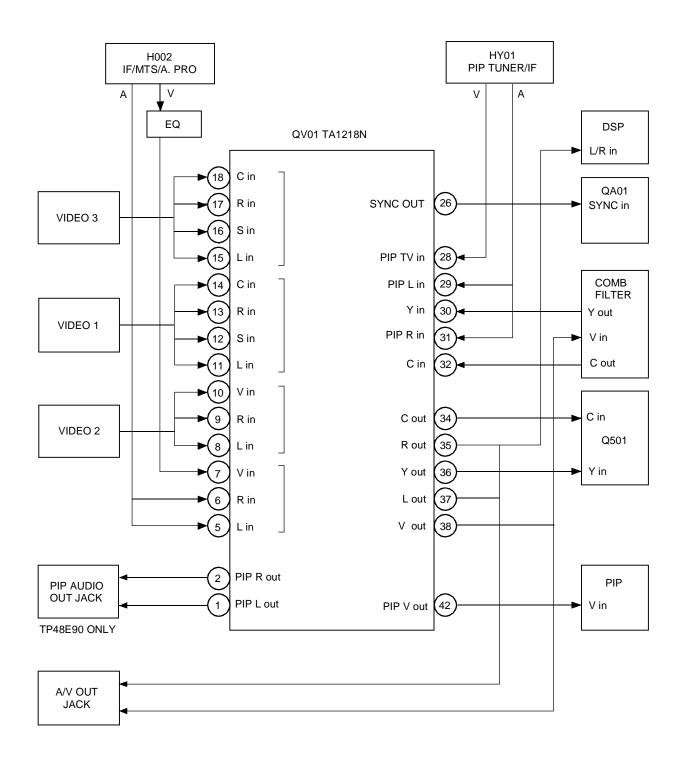

Figure 1-7 illustrates the video signal flow through the TG-1 chassis. The Antenna 1 (ANT 1) and Antenna 2 (ANT 2) inputs allow two separate RF signals to be connected to the RF switcher. When the switch, which is controlled by the microcomputer, QA01, is in the up position the ANT 1 signal is connected to the HY01 PIP Tuner/IF and the H001 Main Tuner. Moving the switch down connects the ANT 2 signal to the H001 Tuner. Due to the RF Switch the ANT 2 signal can't be used as the PIP source, but when ANT 2 is selected the ANT 1 signal is available at RF OUT. The PIP Tuner/IF produces a composite video (CV) signal and sends it to the AV Switcher, QV01. An IF signal produced by the Main Tuner is sent to H002, which produces a composite video signal and sends it to the AV Switcher.

Three video inputs, video 1 through 3, are applied to the AV Switcher. The video 1 input can be composite video, Y/C video, or the test signal from QA01. Video 2 is composite video only, and video 3 is either composite video or Y/C video. A mechanical switch on the video 1 input defaults to the test signal, so a video connector must not be plugged

into the video 1 input jack when the internal test signals are used.

The selected video signal is output as composite video and applied to the video output jack, the EDS/CC/RGB SW., and the Digital Comb Filter or the 3D - Y/C circuit. After processing the video signal is sent back to the AV Switcher as separate luminance (Y) and chrominance (C) signals. The Y and C signals are then sent to Q501 the Video Chroma Deflection Processing IC. A sync signal is tapped off the Y signal and applied to Q501. Q501 processes the video signal and sends separate R, G, and B signals to the CRT drives and the CRTs.

If the PIP feature is selected, composite video from AV Switcher is sent to the PIP circuit, ZY01. After processing, the PIP signal is sent to Q501 as R, G, B, and YS where it is mixed with the main video.

On screen display (OSD) R, G, and B signals produced by the Microcomputer, QA01, are mixed with the Extended Data Service (EDS) and Closed Caption (CC) data in UM01. These new signals are applied to an OR gate, QB91, and combined with the convergence signals from the digital convergence circuit. The convergence signals can be either the customer convergence cross hairs, or the service cross hatch pattern. All of these signals are sent to Q501 where they are mixed with the main video signal.

Figure 1-7 Video Signal Flow Block Diagram

1-10

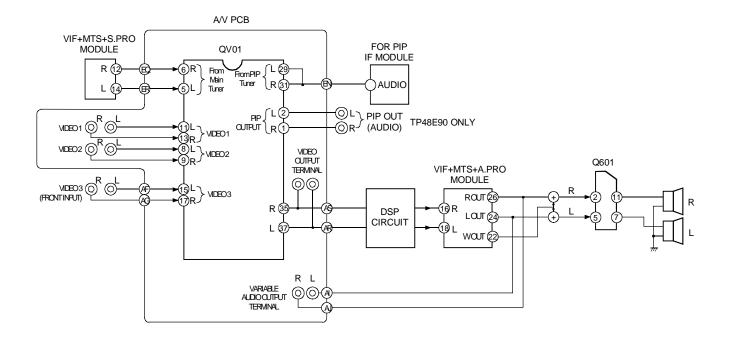

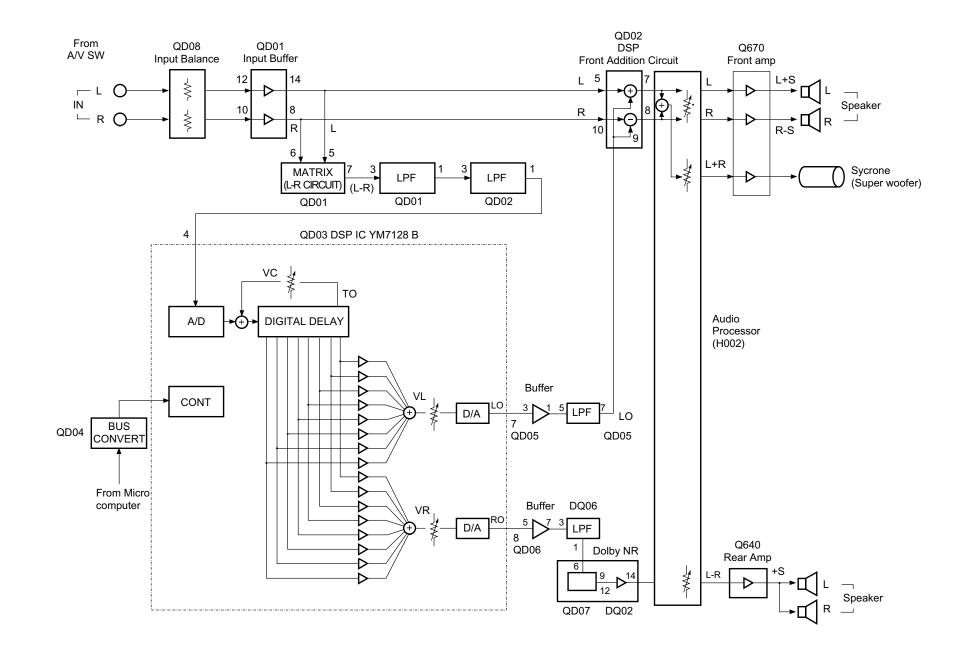

#### 9. AUDIO SIGNAL FLOW BLOCK DIAGRAM

#### **Audio Signal Flow**

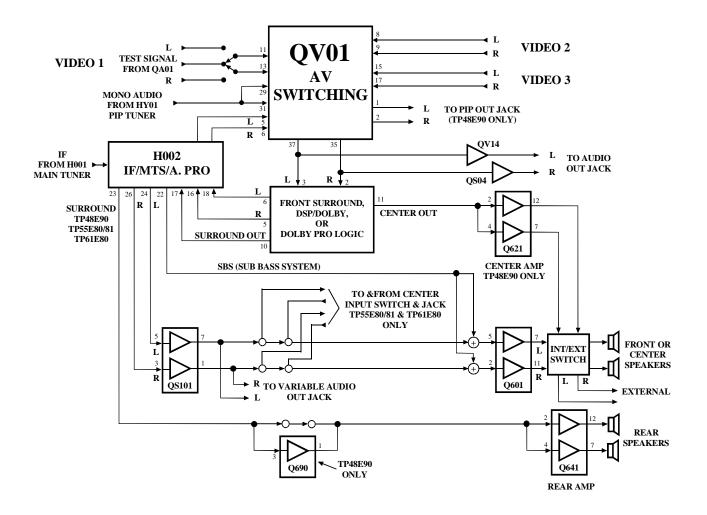

Audio signals are applied to the AV Switcher from the three video jacks, H002, and the PIP Tuner, as shown in Figure 1-8. Like the video signal, there must not be a connector in the video 1 jack for the audio test signal to be applied to the AV Switcher. In the TP48E90, PIP audio is applied to the PIP output jack. The main audio signals are applied to the audio output jacks and to the Front Surround circuit, the DSP/Dolby circuit, or the Dolby Pro Logic circuit. Afterprocessing, the left and right audio signals are applied to the audio processor in H002 where the volume, balance, treble, and bass are controlled. Next, the audio signals are amplified by QS101 and applied to the variable output jacks, and Q601. If the sub bass system (SBS) is selected, a signal is mixed with the left and right signals just before Q601 to increase the signals bass response. In TP55E80/81 and TP61E80 models, the jumper is removed so a center signal can be switched in to replace the main left and right signals. The amplified left and right audio signals are applied to the internal/external speaker switch and routed to the desired speakers.

Sets equipped with Dolby or Dolby Pro Logic have a surround audio signal that is sent to the audio processor in H002 from the Dolby circuit. The surround signal is then sent to the rear amplifier, Q641, amplified, and applied to the rear speakers. In the TP48E90 the surround signal is routed through an amplifier in Q690 before it is applied to Q641. Also, the TP48E90 is equipped with Dolby Pro Logic, and has a center channel. The center channel is amplified by the Center Amplifier, Q621, and applied to the front speakers through the internal/external speaker switch.

Figure 1-8 Audio Signal Flow Block Diagram

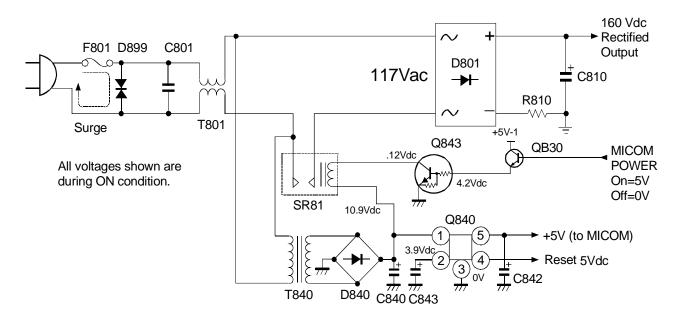

#### 10. POWER SUPPLY AND PROTECTION BLOCK DIAGRAM

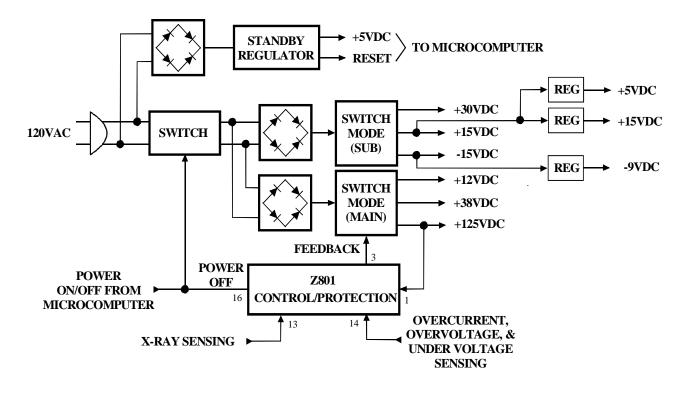

The E model PTVs actually have three separate power supplies as shown in Figure 1-9. These supplies consist of the Standby Supply, the Main Switch Mode Supply, and the Sub Switch Mode Supply. The Standby Supply provides the 5 VDC needed to run the microcomputer and the customer interface controls, such as the key pad and the IR receiver. When the set is turned on, the switch closes to activate the two switch mode supplies and provide the numerous DC voltages needed to operate the set. The Control/Protection circuit, Z801, has two functions. The first is to regulate the Main Switch Mode Supply, and the second is to monitor over current, over voltage, and under voltage sensors throughout the set. If any one of these sensors activates the protection circuit, Z801 turns off the switch powering the two switch mode supplies thus turning off the set. If this occurs, a red LED on the front panel flashes at half second intervals, and the set must be unplugged to reset Z801.

Figure 1-9 Power Supply/Protection Block Diagram

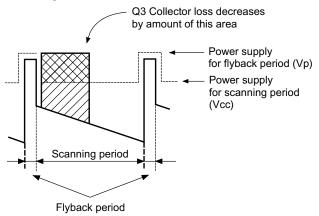

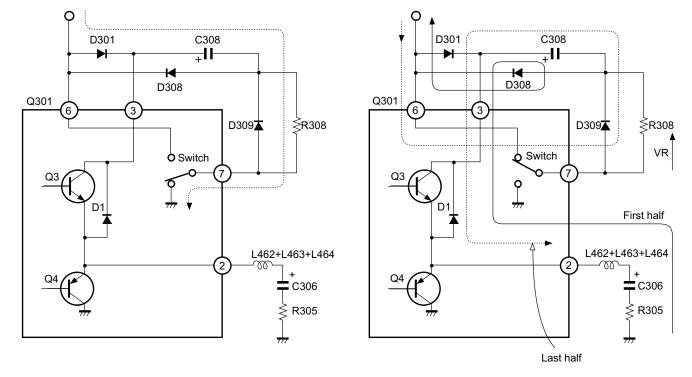

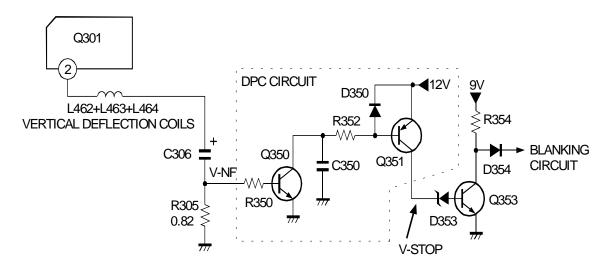

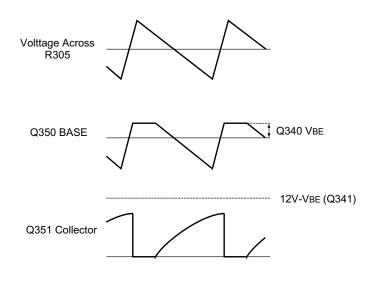

#### 11. HORIZONTAL AND VERTICAL DEFLECTION

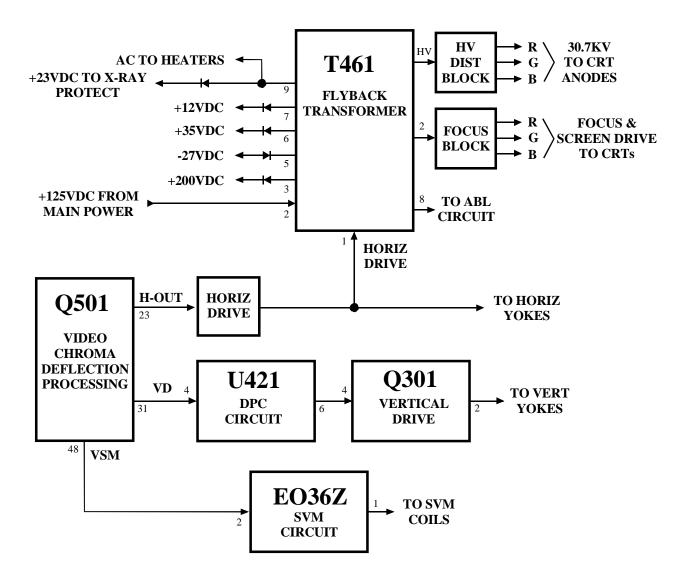

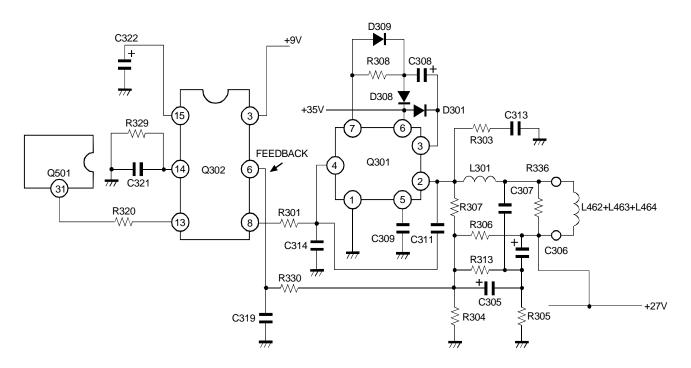

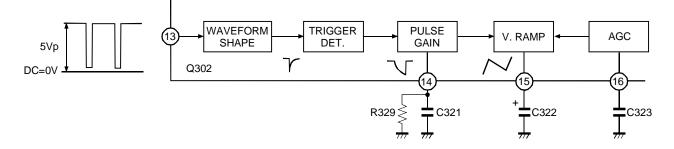

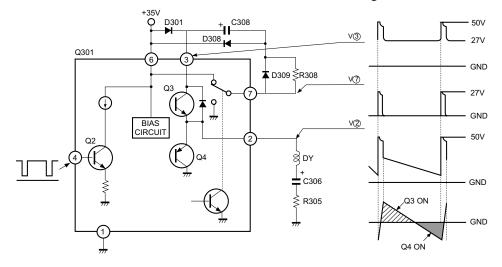

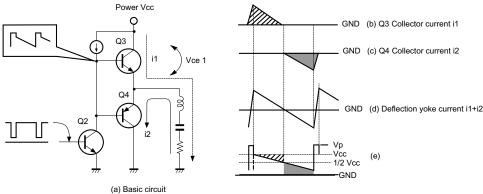

Deflection circuitry in the E model PTV's is rather straight forward as show in Figure 1-10. The horizontal pulse from Q501 drives the horizontal drive circuitry, which in turn drives the Horizontal Yokes and the Flyback Transformer, T461. Numerous low voltage DC supplies are produced by the Flyback, as well as the high voltages for the anode, focus, and screen drives. To prevent excessive high voltages, a sample X-Ray protection voltage is monitored by the over voltage protection circuits. Vertical drive (VD) is applied to the DPC circuit, U421, to correct any distortions before it's sent to the Vertical Drive circuit, Q301. Then the vertical drive circuit supplies the signals required by the yokes for deflection.

To enhance horizontal transitions between dark and light areas of the picture, a Velocity Scan Modulation (VSM) signal is produced by Q501. This signal is sent to the SVM circuit, E036Z, which in turn drives the SVM coils on the CRTs.

Figure 1-10 Horizontal and Vertical Deflection Block Diagram

#### 12. I<sup>2</sup>C Communications

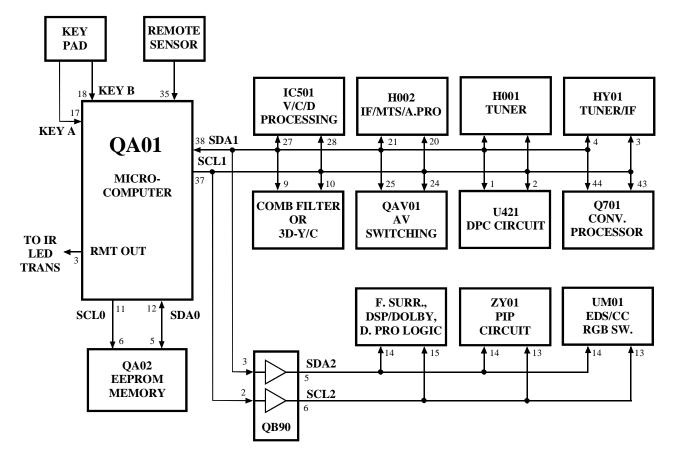

The TG-1 chassis uses I<sup>2</sup>C data communications to control all customer features and most of the service adjustments that where previously done with discrete devices, refer to Figure 1-11. All communications are controlled by the Microcomputer, QA01 through serial data lines (SDA) and serial clock lines (SCL). Memory settings for customer controls and service adjustments (except convergence data) are stored in the E<sup>2</sup>PROM Memory, QA02, and communicated to QA01 by the SCL0 and SDA0 lines. Data and clock lines SDA1 and SCL1 communicate with most of the circuits in the set. However, there are three plug in circuits where the data and clock signals are buffered by QB90 to provide isolation.

All customer functions and most services adjustments are implemented through the Key Pad and the Remote Sensor. The RMT OUT signal on the microcomputer drives the IR Transmitter on the front panel, but it's only used in the manufacturing process. Figure 1-12 shows the Service Registers and their default values used for making adjustments in the set.

| REG  | ADJUSTMENT            | PRESET |

|------|-----------------------|--------|

| RCUT | RED CUTOFF            | 40     |

| GCUT | GREEN CUTOFF          | 40     |

| BCUT | BLUE CUTOFF           | 40     |

| RDRV | RED DRIVE             | 40     |

| BDRV | BLUE DRIVE            | 40     |

| CNTX | SUB-CONTRAST MAX      | 7F     |

| BRTC | SUB-BRIGHT CENTER     | 80     |

| COLC | SUB-COLOR CENTER      | 50     |

| TNTC | SUB-TINT CENTER       | 40     |

| SCOL | SAP-COLOR             | 15     |

| SCNT | SUB-CONTRAST          | 15     |

| HPOS | HORIZ. POSITION       | 16     |

| VPOS | VERTICAL POSITION     | 00     |

| HIT  | VERTICAL HEIGHT       | D1     |

| GMPS | GMPS                  | 00     |

| VLIN | VERTICAL LINEARITY    | 12     |

| VSC  | A-S CORRECTION        | 08     |

| VPS  | VERTICAL SHIFT        | 15     |

| VCP  | V-COMPENSATION        | 03     |

| WID  | PICTURE WIDTH         | 25     |

| TRAP | TRAPEZIUM             | 10     |

| HCP  | H-COMPENSATION        | 02     |

| VFC  | V-F CORRECTION        | 0F     |

| STRH | HORIZ. START POSITION | 82     |

Figure 1-12 Service Register Default Values

Figure 1-11 I<sup>2</sup>C Communication Block Diagram

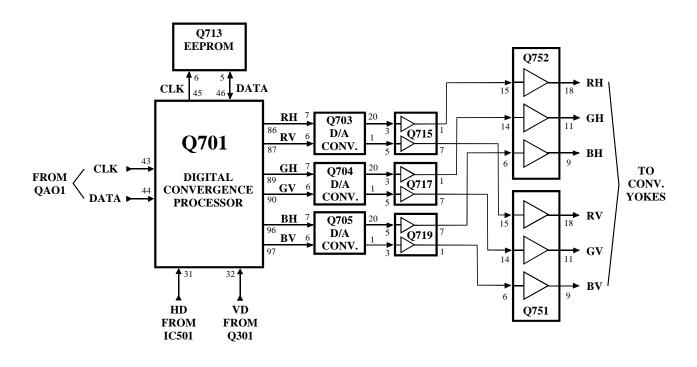

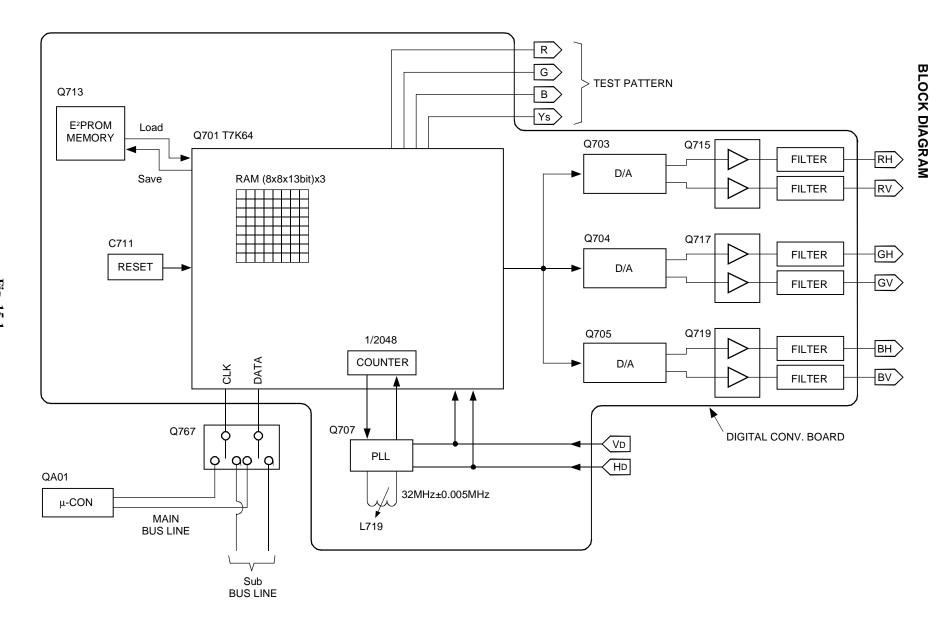

#### **13. Digital Convergence**

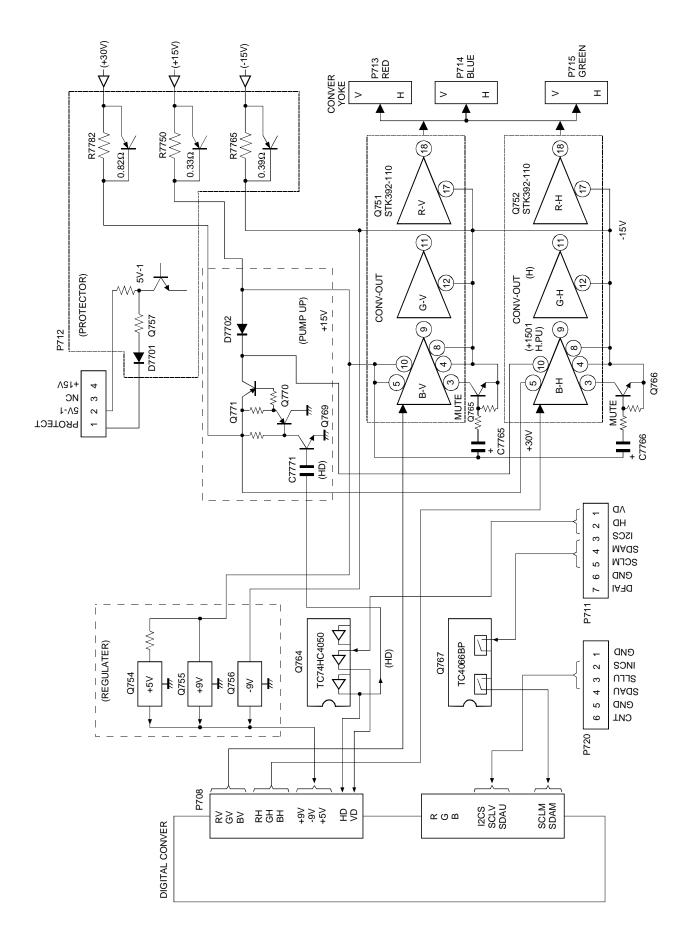

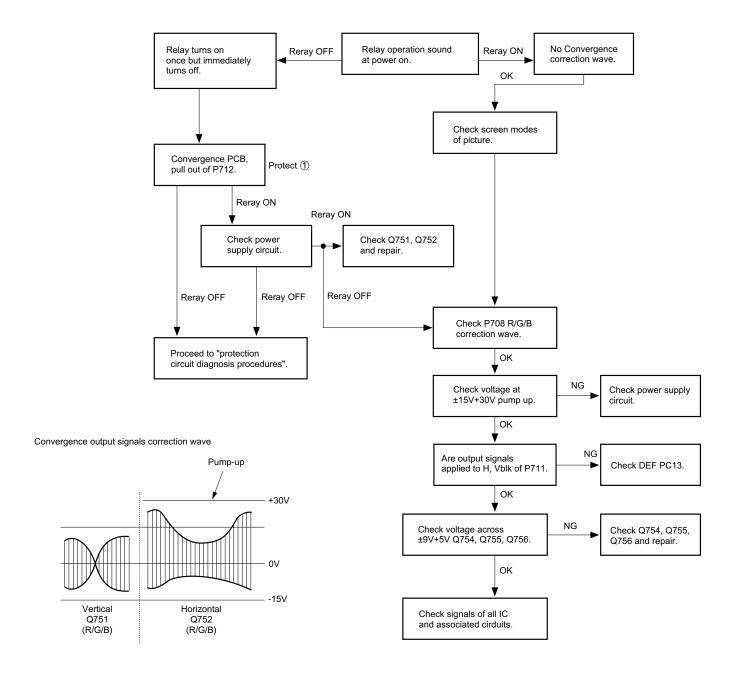

The TG-1 model PTV's are equipped with a new digital convergence circuit shown in Figure 1-13. This circuit allows servicers to set the convergence with the remote control. Q701, the Digital Convergence Processor aligns the convergence from data received from the remote, and saves the settings in the E<sup>2</sup>PROM, Q713. The digital convergence signals are converted to analog by the D/A Converters Q703, Q704, and Q705. Then they are amplified

by the pre amps (Q715, Q717, & Q719) and power amps (Q751 & Q751) before being applied to the convergence yokes. The Power Amps Q752 and Q751 dissipate allot of heat because of their current draw, so the supplies to these amps have a number of sensors for over current conditions. Most of the convergence circuit is on a shielded board, but the power amps are easily accessible for service.

Figure 1-13 Convergence Block Diagram

## LAB 1

#### **BASIC OPERATION AND UNIT UNDERSTANDING**

As a servicer, it is important now, more than ever, to fully understand the operation and functions of a television set before proceeding with a repair. This is because many of the problems encountered by a customer today can be caused by an incorrect menu selection or improper setup.

Therefore, the purpose of this lab is to familiarize you with menus and features of the television from the customer's point of view.

#### SECTION ONE BASIC OPERATION

- 1. Verify that the unit is connected to an AC supply, and that a signal is connected to the ANT 1 input. While verifying signal connections, take time to examine all of the inputs on the rear and front (behind door) of the unit.

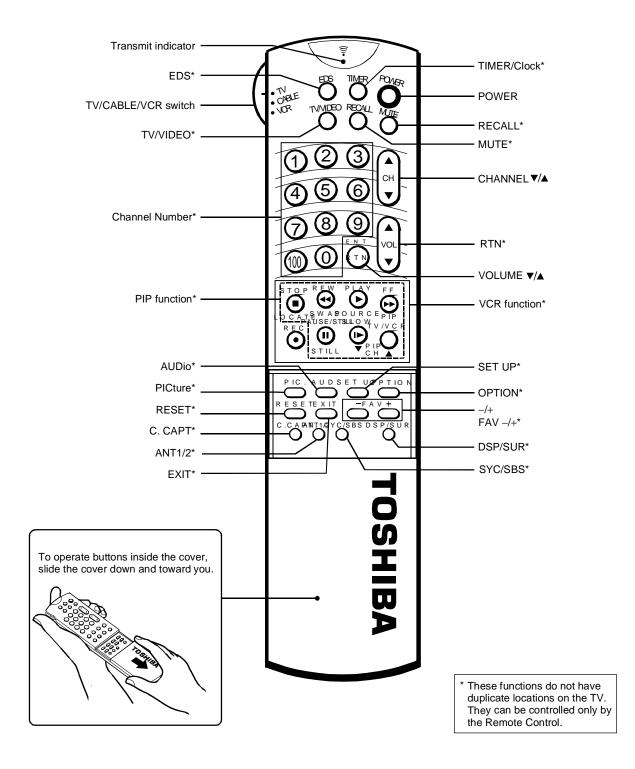

- 2. Turn on the set with the remote control and tune to an active channel. Refer to page 9 of the service manual provided and familiarize yourself with all of the keys on the remote paying, particular attention to the following keys:

- EDSTIMERPIP Functions

Open the bottom door on the remote control by sliding it down. Try each key starting with the upper row. Each of these buttons brings up another menu and/or sub-menus.

3. In the *Picture Menu*, What is <u>Color Temperature</u>?

4. In the Audio Menu, Where can the speakers be turned off by the user?

5. In the Setup Menu, What is Favorite Channel?, What is Channel Lock?

- 6. Refer to page 16 of the Service Manual and perform the *User Convergence Adjustments*. How is this different from previous Toshiba PJTVs?

- 7. In the *Option Menu*, How many different languages are there? What are they used for? What is <u>Channel Label</u> Used for?

#### **NOTES:**

#### SECTION TWO DISASSEMBLY & SERVICE POSITION

Follow the procedure listed below to gain access to the tubes and circuit boards.

- 1. Remove the speaker grill by holding the sides and pulling straight out.

- 2. Take out the four screws holding the plastic shield in place. Then remove the shield.

- 3. Remove the control wires from the holder on the metal shield in front of the CRTs.

- 4. Remove the 4 screws holding the metal shield in place. The shield is notched, so slide it to the right then down to remove it.

- 5. Remove the two screws holding the front control panel. Then release the tabs on either side and let it hang down out of the way.

- 6. Remove the 4 screws holding the bottom of the screen. Then lift up on the top of the screen and pull it away from the cabinet.

- 7. Remove the 5 screws holding the back panel. Then remove the back panel.

- 8. Reattach the control panel to the light box.

- 9. Remove the six screws on the front of the light box.

- 10. Remove the three screws on the back of the cabinet.

- 11. Remove the one screw holding the back of the light box to the cabinet.

- 12. From the front of the set, lift the light box up just a little, and pull it towards you.

- 13. Pull the light box all the way out of the cabinet and turn it on its side.

CAUTION: the light box weighs about 85 pounds, so get help if you need it.

## SECTION THREE IDENTIFICATION

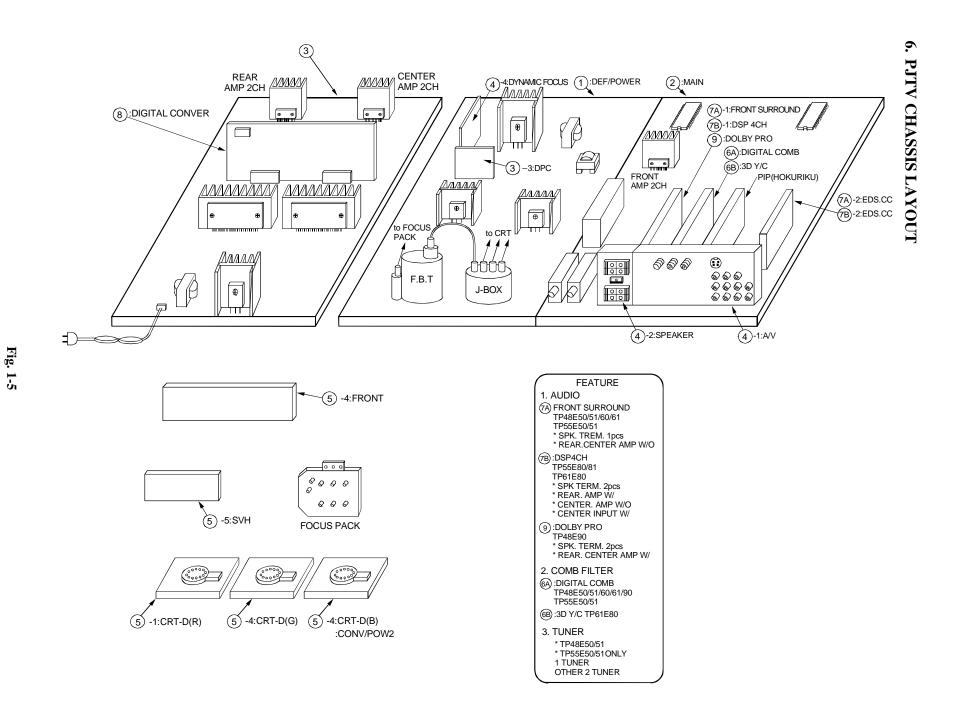

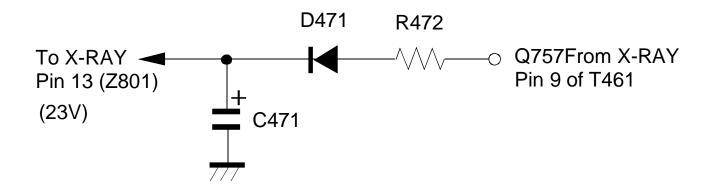

- 1. Identify each of the board assemblies and note their locations. Use Figure 1-5 to help you identify the various boards.

- □ Convergence/Output/Power Board

- **Deflection/Power Board**

- □ Main PCB

- □ Front Surround Board

- **Digital Comb Filter Board**

- **D PIP Board**

- □ EDS/CC Board

- 2. Is there a convergence board in this unit? If so, where?

- 3. How does this convergence setup differ from previous models?

- 4. Examine the Flyback and HV lead assemblies. What is different about this area from earlier models?

- 5. Is it possible for one technician to perform a service call on this type of unit?

- 6. Put the lightbox in the cabinet, but don't screw it in. Then replace the screen and control panel. Use a few screws to hold the screen and control panel in place.

#### SUMMARY

In this lab, the operation and function of the unit was determined, and the unit was set up for service on the bench. Common user type problems in addition to overall serviceability was also discussed.

#### END OF LAB 1

## **LAB 2**

#### TEST SIGNALS, SELF DIAGNOSTICS, & SERVICE REGISTERS

**OBJECTIVES:** After completing this lab you will be able to:

- 1. Enter and exit the set's internal video and audio test signals.

- 2. Use the test signals for troubleshooting.

- 3. Use the set's self diagnostic feature.

- 4. Make adjustments in the set with the service registers via the remote control.

#### SECTION ONE VIDEO TEST SIGNALS

- 1. Verify that the unit is connected to an AC supply, and that a signal is connected to the ANT 1 input.

- 2. Enter the service mode by pressing mute on the remote. Press and hold mute a second time while pressing menu on the control panel. An S appears in the upper right corner of the screen indicating that the set is in the service mode. Press menu and the RCUT register appears in the upper left corner of the screen.

- 3. Push the TV/VIDEO button on the remote once to enter the internal test pattern mode. The screen should be red.

- 4. Slowly cycle through the test signals with the TV/VIDEO button until the white cross hairs on a black background appear. (If the TV/VIDEO button is pushed in rapid succession, the set will jump out of the test signal mode to one of the inputs ANT 1, VIDEO 1, VIDEO 2, or VIDEO 3. The set is still in the service mode, so if this occurs, push the menu button then the TV/VIDEO button to get back into the test signal mode.)

- 5. Plug a video cable into the VIDEO 1 input jack (make sure the other end of the cable is not plugged into a video source)

- 6. What happened to the cross hairs?

- 7. If something did happen to the cross hairs, why did it happen?

- 8. Is there video on the screen?

- 9. If there is video on the screen, where does it come from?

10. Unplug the video cable.

#### SECTION TWO AUDIO TEST SIGNALS

- 1. Push the 8 button on the remote to activate the audio test signal. (**NOTE:** The internal test pattern mode must be activated for this feature to work.)

- 2. Push the mute button twice. Now you can control the volume of the signal.

- 3. Select AUD on the remote control.

- 4. Select BALANCE and adjust it from left to right with the + and buttons.

- 5. Select SPEAKERS and turn them off then on. (**NOTE:** The speakers are turned off at Q601, refer to Figure 1-8, while the volume, bass, treble, and balance are controlled in H002. This means you can troubleshoot most of the audio system with the speakers off.)

- 6. Plug an audio cable into the left AUDIO 1 input jack (make sure the other end of the cable is not plugged into an audio source)

- 7. What happened to audio?

- 8. If something did happen to the audio, why did it happen?

9. Push the 8 button to turn off the audio test signal.

10. Cycle the video test signals back to the ANT 1 signal with the TV/VIDEO button.

#### SECTION THREE SELF DIAGNOSTICS

- 1. Push the 9 button to activate the self diagnostic feature.

- 2. What does POWER indicate?

3. What does BUS LINE indicate?

- 4. What does BUS CONT indicate?

- 5. What does BLOCK indicate?

- 6. Push the EXIT button to exit the self diagnostic feature.

- 7. Select the VIDEO 1 input with the TV/VIDEO button. (Make sure there is no signal applied to VIDEO 1)

- 8. Push MENU on the control panel to display the registers.

- 9. Push 9 to activate the self diagnostic feature.

- 10. Is the display different from the previous display.

- 11. If it is, explain why.

- 12. Push the EXIT button to exit the self diagnostic feature.

- 13. Push MENU on the control panel to display the registers.

#### SECTION FOUR SERVICE REGISTERS

**NOTE:** In each of the following exercises write down the register's value before adjusting it. Then restore the register to its original value before proceeding to the next exercise.

1. Enter the internal test pattern mode and select the test signal that has a white window in the upper center of a black background as shown below.

2. Increase the RCUT register value and describe its effect on the picture.

RCUT\_\_\_\_\_

3. Change the test signal to the white on black cross hatch pattern as shown below.

|  |  |  |  |  | ī |

|--|--|--|--|--|---|

|  |  |  |  |  | П |

|  |  |  |  |  | Γ |

|  |  |  |  |  | П |

|  |  |  |  |  | E |

|  |  |  |  |  |   |

|  |  |  |  |  |   |

|  |  |  |  |  |   |

|  |  |  |  |  |   |

|  |  |  |  |  | Г |

|  |  |  |  |  | 1 |

4. Select the HPOS register and vary its value between 00 and 1F. Describe its effect on the picture. What happens if you increase the register to 20?

HPOS\_\_\_\_\_

5. Select the VPOS register and vary its value between 00 and 07. Describe its effect on the picture. What happens if you increase the register to 08?

VPOS\_\_\_\_\_

6. Select the HIT register and vary its value 5 steps above and below the recorded value. Describe its effect on the picture.

|        | HIT                                                                                                                         |

|--------|-----------------------------------------------------------------------------------------------------------------------------|

|        |                                                                                                                             |

| 7.     | Select the VLIN register and vary its value 8 steps above and below the recorded value. Describe its effect on the picture. |

|        | VLIN                                                                                                                        |

|        |                                                                                                                             |

| 8.     | Select the WID register and vary its value 8 steps above and below the recorded value. Describe its effect on the picture.  |

|        | WID                                                                                                                         |

|        |                                                                                                                             |

| 9.     | Select the STRH register and vary its value 8 steps above and below the recorded value. Describe its effect on the picture. |

|        | STRH                                                                                                                        |

|        |                                                                                                                             |

| [ ]]N/ | IMARY                                                                                                                       |

Now that you have completed Lab 2, you should be able to use the internal video and audio test signals, the self diagnostic feature, and the service registers for making adjustments.

#### END OF LAB 2

## SECTION II TUNER, IF/MTS/S.PRO MODULE

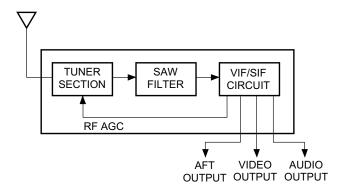

#### **1. CIRCUIT BLOCK**

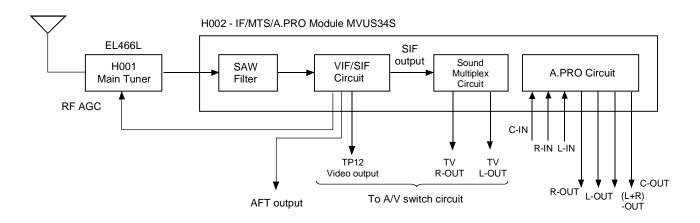

Fig. 2-1 Block diagram

#### 1-1. Outline

- (1) RF signals sent from an antenna are converted into intermediate frequency band signals (video: 45.75 MHz, audio: 41.25 MHz) in the tuner. (Hereafter, these signals are called IF signals.)

- (2) The IF signals are band-limited in passing through a SAW filter.

- (3) The IF signals band-limited are detected in the VIF circuit to develop video and AFT signals.

- (4) The band-limited IF signals are detected in the SIF circuit and the detected output is demodulated by the audio multiplexer, developing R and L channel outputs. These outputs are fed to the A/V switch circuit.

- (5) A sound processor (S.PRO.) is provided.

#### 1-2. Major Features

- (1) The VIF/SIF circuit is fabricated into a small module by using chip parts considerably.

- (2) As the tuner, EL466L that which contains an integrated PLL circuit is employed.

- (3) Wide band double SAW filter F1802R used.

- (4) FS (frequency synthesizer) type channel selection system employed.

- (5) VIF/SIF circuit uses PLL sync detection system to improve performances shown below:

- Telop buzz in video over modulation

- DP, DG characteristics (video high-fidelity reproduction)

- Cross color characteristic (coloring phenomenon at color less high frequency signal objects)

- (6) HIC SBX1637A-22 is used in the audio multiplexer circuit to minimize the size with increased performance.

- (7) As a sound control processor, TA1217N is used. I<sup>2</sup>Cbus data control the DAC inside the IC to perform switching of the audio multiplexer modes.

#### 1-3. Audio Multiplex Demodulation Circuit

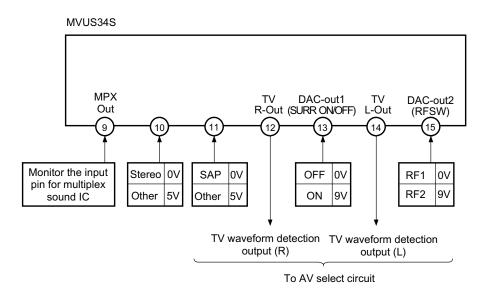

The sound multiplex composite signal FM-detected in the PIF circuit enters pin 12 of HIC (hybrid IC) in passing through the separation adjustment VR RV2 and amplified. After the amplification, the signal is split into two: one enters a de-emphasis circuit, and only the main signal with the L-R signal and a SAP signal removed enters the matrix circuit. At the same time, the other passes through various filters and trap circuits, and the L-R signal is AM-demodulated, and the SAP is FM-demodulated.

Then, both are fed to the matrix circuit. At the same time, each of the stereo pilot signal fH and the SAP pilot signal 5fH is also demodulated to obtain an identification voltage. With the identification voltage thus obtained and the user control voltage are used to control the matrix.

The audio signals obtained by demodulating the sound multiplex signal develop at pin 10 and 11 of HIC and develop the terminals of 12 and 14 of the module.

Fig. 2-2 Block diagram of MVUS34S

| Dunad            | Carritalia a      | Output OSD display |               | lisplay |     |

|------------------|-------------------|--------------------|---------------|---------|-----|

| Broad-<br>casted | Switching<br>mode | 12 pin<br>(R)      | 14 pin<br>(L) | Stereo  | SAP |

| Stereo           | STE               | R                  | L             | Y       | Ν   |

|                  | SAP               | R                  | L             | Y       | Ν   |

|                  | MONO              | L+R                | L+R           | Y       | Ν   |

| Mono             | STE               | L+R                | L+R           | N       | Ν   |

|                  | SAP               | L+R                | L+R           | N       | Ν   |

|                  | MONO              | L+R                | L+R           | N       | Ν   |

| Stereo           | STE               | R                  | L             | Y       | Y   |

| +                | SAP               | SAP                | SAP           | Y       | Y   |

| SAP              | MONO              | L+R                | L+R           | Y       | Y   |

| Mono             | STE               | L+R                | L+R           | N       | Y   |

| +                | SAP               | SAP                | SAP           | N       | Y   |

| SAP              | MONO              | L+R                | L+R           | N       | Y   |

Table 2-1 Matrix for broadcasting conditions and reception mode

Note:

Of the mode selection voltages, switching voltages for STE, SAP, MONO do not output outside the module. They are used inside the module to control the BUS.

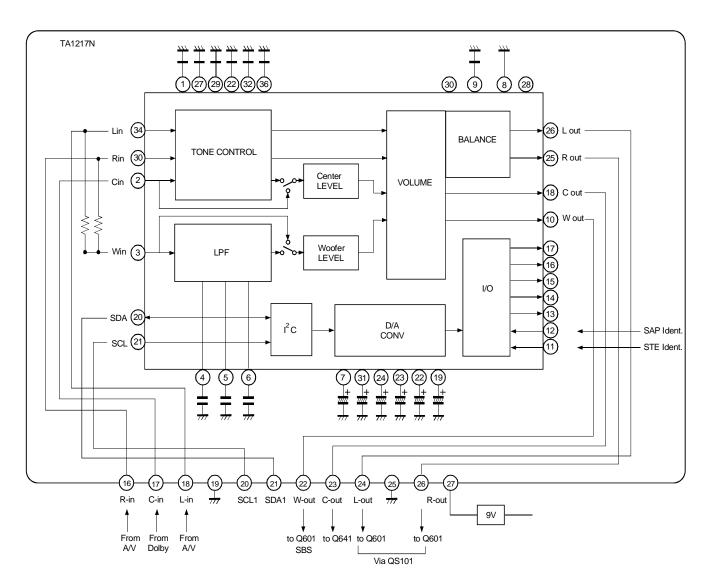

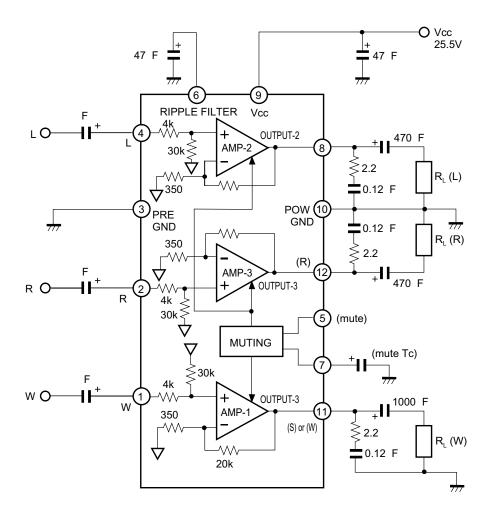

#### 1-4. A.PRO Section (Audio Processor)

The S.PRO section has following functions.

- (1) Woofer processing (L+R output)

- (2) High band, low band, balance control

- (3) Sound volume control, cyclone level control

- (4) Cyclone ON/OFF

All these processing are carried out according to the BUS signals sent from a microcomputer.

Fig. 2-3 shows a block diagram of the A.PRO IC.

Fig. 2-3 A.PRO block diagram

Configuration of the audio circuit and signal flow are given in Fig. 2-4

Fig. 2-4

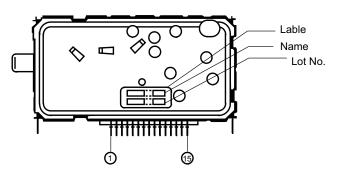

#### **2. PIP TUNER**

Fig. 2-5

#### 2-1. Outline

The PIP tuner (EL922L) consists of a tuner and an IF block integrated into one unit. The tuner receives RF signals induced on an antenna and develops an AFT output, video output, and audio output.

The tuner has receive channels of 181 as in the tuner for the main screen and it is also controlled through the I2C-bus. As the IC for the IF, a PLL complete sync detection plus

audio inter carrier system are employed.

| Terminal No. | Name    |

|--------------|---------|

| 1            | NC      |

| 2            | 32V     |

| 3            | S-CLOCK |

| 4            | S-DATA  |

| 5            | NC      |

| 6            | ADDRESS |

| 7            | 5V      |

| 8            | RF AGC  |

| 9            | 9V      |

| 10           | AUDIO   |

| 11           | GND     |

| 12           | AFT     |

| 13           | NC      |

| 14           | GND     |

| 15           | VIDEO   |

Fig. 2-6 Tuner terminal layout

## SECTION III CHANNEL SELECTION CIRCUIT

## 1. OUTLINE OF CHANNEL SELECTION CIRCUIT SYSTEM

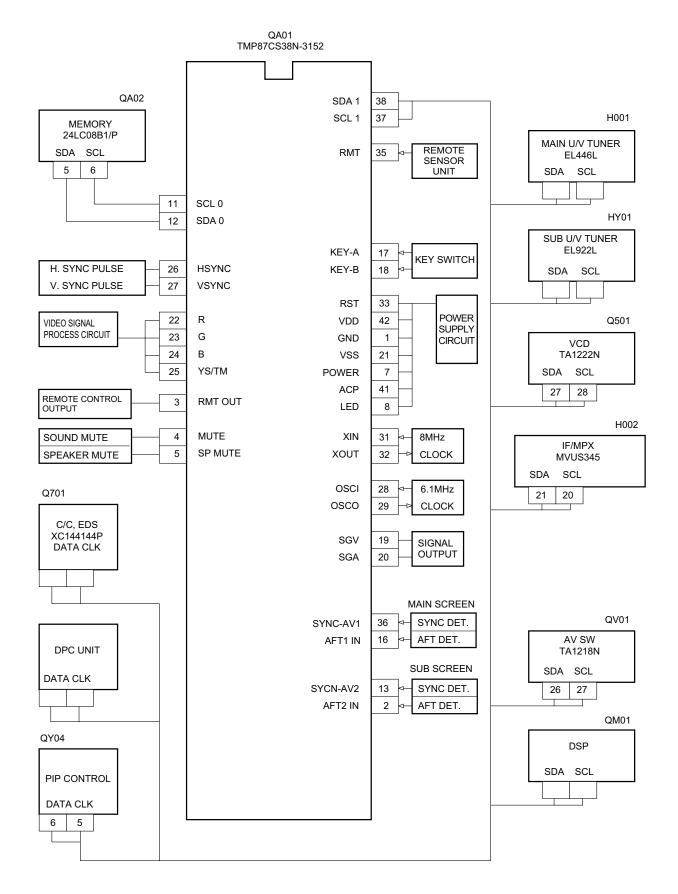

The channel selection circuit in the N5SS chassis employs a bus system which performs central control by connecting a channel selection microcomputer to a control IC in each circuit block through control lines called a bus. This bus system herin referred to as the I<sup>2</sup>C bus system (two line bus) is licensed from and was developed by Philips.

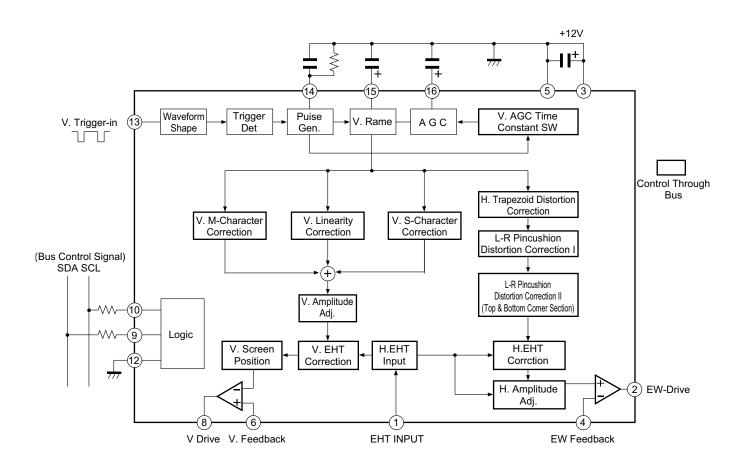

Integrated circuits controlled by the I<sup>2</sup>C bus system are : QN06 for audio signal processing, Q501 for V/C/D signal processing , QV01 for A/V switching, QA02 for non volatile memory, main and sub U/V tuners (H001, HY01), Q302 for deflection distortion correction, QY04 for PIP signal processing, QM01 for DSP, and Q701 for closed caption control.

Differences from the previous N5SS chassis include;

- 1. On-screen display generation now originates within ICA01. A separate IC is no longer used.

- 2. The microcomputer does not perform the closed caption function, but instead controls a separate IC for this purpose.

- 3. The system uses two sperate channels of I<sup>2</sup>C bus. One of these is dedicated for communication with the non-volatile memory.

### 2. OPERATION OF CHANNEL SELECTION CIRCUIT

An 8 bit, Toshiba microcomputer (series TLCS-870) is used within the television as ICA01. Part number TMP87CS38N-3152 or similar is employed.

With this microcomputer, each IC and circuit shown below are controlled.

- (1) CONTROL OF AUDIO SIGNAL PROCESS IC (QN06 Toshiba TA1217N)

- Adjustments for volume, treble, bass and balance

- Selection between surround mode and DSP mode, and level adjustment

- Level adjustment of BAZOOKA (Sub-Bass) system

- Audio muting during channel selection or no signal reception.

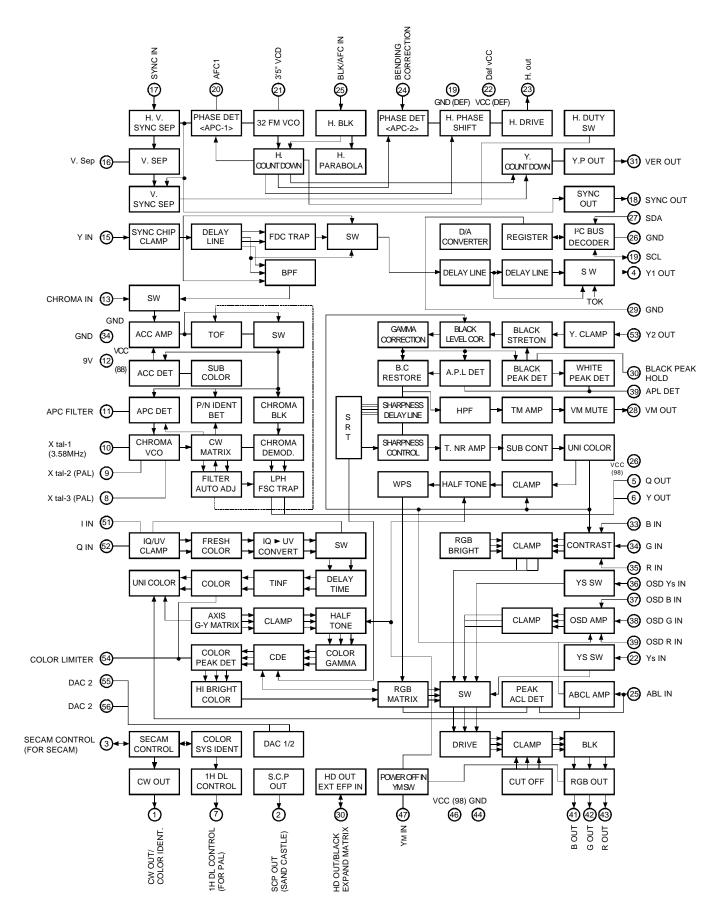

- (2) CONTROL OF VIDEO/CHROMA/DEF SIGNAL PROCESS IC (Q501 Toshiba TA1222N)

- Adjustments for uni-color, brightness, tint, color gain, sharpness and PIP uni-color

- Setting of adjustment memory values for subbrightness, sub-color and sub-tint, etc.

- Setting of memory values for video parameters such as white balance (RGB cutoff, GB drive) and gcorrection, etc.

- Setting of video parameters of video modes (Standard, Movie, Memory)

- (3) CONTROL OF A/V SWITCH IC (QV01 Toshiba TA1218N)

- Preforms source switching for main screen and sub screen

- Performs source switching for TV and up to three video inputs

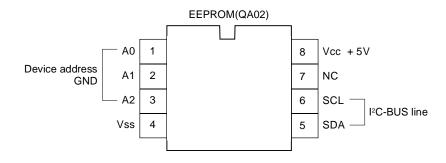

- (4) CONTROL OF NON-VOLATILE MEMORY IC (QA02 Microchip 24LC08BI/P)

- Memorizes data for video and audio signal adjustment values, volume and woofer adjustment values, external input status, etc.

- Memorizes adjustment data for white balance (RGB cutoff, GB drive), sub-brightness, sub color, sub tint, etc.

- Memorizes deflection distortion correction value data adjusted for each unit.

- (5) CONTROL OF U/V TUNER UNIT (H001 Matsushita EL466L, HY01 Toshiba EL922L)

- A desired channel can be tuned by transferring a channel selection frequency data (divided ratio data) to the I<sup>2</sup>C bus type frequency synthesizer equipped in the tuner, and by setting a band switch which selects the UHF or VHF band.

- (6) CONTROL OF DEFLECTION DISTORTION CORRECTION IC (Q302 Toshiba TA8859P)

- Sets adjustment memory value for vertical amplitude, linearity, horizontal amplitude, parabola, corner, trapezoid distortion.

- (7) CONTROL OF PIP SIGNAL PROCESS IC (QY04 Toshiba TC9083F)

- Controls ON/OFF and position shift of PIP.

- (8) CONTROL OF DIGITAL SOUND PROCESSOR IC (QM04 Yamaha YSS238-D)

- Performs mode switching of DSP.

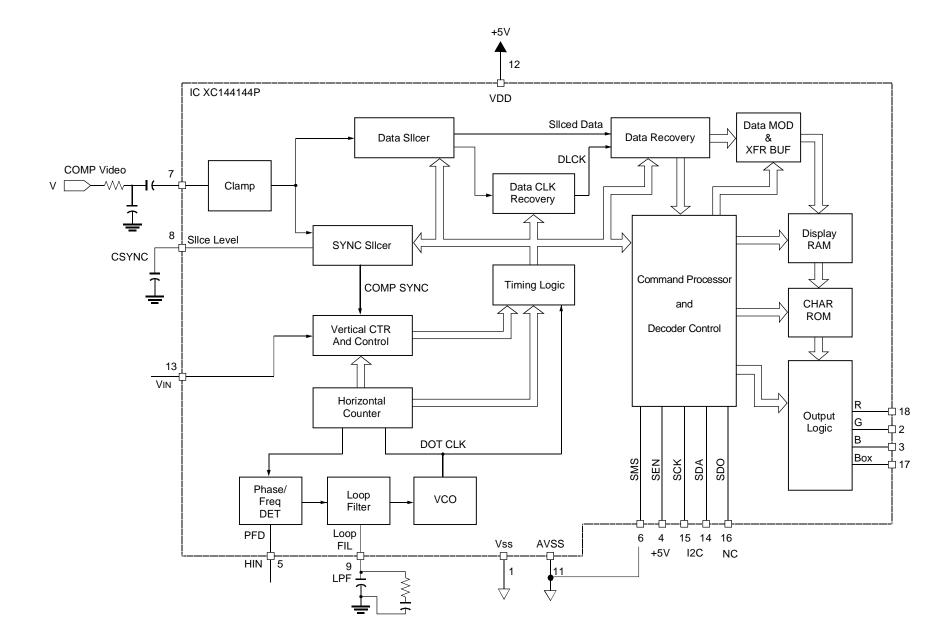

- (9) CONTROL OF CLOSED CAPTION/EDS (QM01 Motorola XC144144P)

- Controls Closed Caption/EDS.

### **3. MICROCOMPUTER**

The main Microcomputer TMP87CS38N-3152 has 60k byte of ROM capacity and is equipped with an internal OSD function.

The specification is as follow.

- Type name : TMP87CS38N-3152

- ROM : 60k byte

- RAM : 2k byte

- Processing speed : 0.5m s (at 8MHz with Shortest command)

- Package : 42 pin shrink DIP

- I<sup>2</sup>C-BUS : two channels

- PWM : 14 bit x 1, 7 bit x 9

- ADC : 8 bit x 6 (Successive comparison system, Conversion time 20ms)

- OSD

Character kinds : 256

Character display : 24 characters x 12 lines

- Character dot : 14 x 18 dots

- Character size : 3 kinds (Selected by line)

- Character color : 8 colors (Selected by character)

- Display position : Horizontal 128 steps, Vertical

256 steps

This microcomputer performs the functions of an Analog to Digital converter, reception of U/V TV and OSD display in

one chip.

- IIC device controls through I<sup>2</sup>C bus. (Timing chart : See fig. 3-1)

- Pin 8, (LED) is used to source current and is an output only.

- For clock oscillation, an 8MHz ceramic oscillator is used.

- I<sup>2</sup>C has two channels. One is for EEPROM only.

- A Self diagnosis function which utilizes the ACK function of I<sup>2</sup>C is employed

- Function indication is added to service mode.

- Operation by remote control is possible, and controls and adjustments can be made with no physical contact is possible. (Bus connector in the conventional bus chassis is deleted.)

- Substantial self diagnosis function

- (1) B/W composite video signal generating function (inside micon, green crossbar added)

- (2) Generating function of audio signal equivalent to 1kHz (inside micon)

- (3) Detecting function of power protection circuit operation

- (4) Detecting function of abnormality in I<sup>2</sup>C bus line

- (5) Functions of LED blink indication and OSD indication

- (6) Block diagnosis function which uses new VCD and AV SW

Fig. 3-1

# 4. MICROCOMPUTER TERMINAL FUNCTION

|           |    |    | TMP8/CS38N31         | 52 (QA01) |   |    |           |

|-----------|----|----|----------------------|-----------|---|----|-----------|

|           |    |    |                      |           |   |    |           |

| GND       | 1  |    | GND                  | VDD       |   | 42 | VDD       |

| BAL       | 2  | I  | P40 (PWM0)           | P57       | Ι | 41 | ACP       |

| REM OUT   | 3  | 0  | P41 (PWM1)           | P32       |   | 40 | NC        |

| MUTE      | 4  | 0  | P42 (PWM2)           | P57       |   | 39 | GND       |

| SP MUTE   | 5  | 0  | P43 (PWM3)           | SDA0      | ю | 38 | SDA1 IIC- |

| NC        | 6  | 0  | P44 (PWM4)           | SCL0      | 0 | 37 | SCL1 BUS  |

| POWER     | 7  | 0  | P45 (PWM5)           | (TC3)P31  | Ι | 36 | SYNC AV1  |

| LED       | 8  | 0  | P46 (PWM6)           | (RXIN)P30 | Ι | 35 | RMT IN    |

| NC        | 9  | 0  | P47 (PWM7)           | P20       | Ι | 34 | SW IN     |

| NC        | 10 | I  | P50 (PWM8/TC2) RESET |           | Ι | 33 | RESET     |

|           | 11 | 0  | P51 (SCL1)           | XOUT      | 0 | 32 | XOUT      |

| -BUS SDA0 | 12 | 10 | P52 (SDA1)           | XIN       | Ι | 31 | XIN       |

| SYNC VCD  | 13 | I  | P53 (AINO/TC1)       | TEST      | Ι | 30 | TEST      |

| NC        | 14 | I  | P54 (AIN1)           | 0SC2      | 0 | 29 | 0SC1      |

| AFT2      | 15 | I  | P55 (AIN2)           | 0SC1      | Ι | 28 | 0SC2      |

| AFT1      | 16 | I  | P56 (AIN3)           | VD        | Ι | 27 | VSYNC     |

| KEY-A     | 17 | I  | P60 (AIN4)           | HD        | Ι | 26 | HSYNC     |

| KEY-B     | 18 | I  | P61 (AIN5)           | Y/BL      | 0 | 25 | Ys        |

| SGV       | 19 | 0  | P62                  | В         | 0 | 24 | BOUT      |

| SGA       | 20 | 0  | P63                  | G         | 0 | 23 | GOUT      |

| GND       | 21 |    | VSS                  | R         | 0 | 22 | ROUT      |

|           |    |    |                      |           |   |    |           |

TMP87CS38N3152 (QA01)

Fig. 3-2

## << MICROCOMPUTER TERMINAL NAME AND OPERATION LOGIC >>

| No. | Terminal Name | Function                       | In/Out | Logic                                  | Remarks                      |

|-----|---------------|--------------------------------|--------|----------------------------------------|------------------------------|

| 1   | GND           |                                |        |                                        | 0V                           |

| 2   | BAL           | INPUT BALANCE                  | Out    | PWM out                                |                              |

| 3   | REM OUT       | REMOTE CONTROL<br>SIGNAL OUT   | Out    | Remote control output                  |                              |

| 4   | MUTE          | SOUND MUTE OUT                 | Out    | Sound mute output                      |                              |

| 5   | SP MUTE       | SPEAKER MUTE                   | Out    | In muting = H                          |                              |

| 6   | DEF POW       |                                | Out    |                                        |                              |

| 7   | POWER         | POWER ON/OFF OUT               | Out    | Power control In ON=H                  |                              |

| 8   | LED           | POWER LED OUTPUT               | Out    | Power LED on-control<br>LED lighting=L |                              |

| 9   | POWER LNB     |                                | Out    |                                        | 0V                           |

| 10  | LNB DET       |                                | In     |                                        | 0V                           |

| 11  | SCL()         | IIC BUS CLOCK OUT              | Out    | IIC bus clock output 0                 |                              |

| 12  | SDA()         | IIC BUS DATA IN/OUT            | In/Out | IIC bus data input/output 0            |                              |

| 13  | SYNC VCD      | H SYNC INPUT                   | In     | Main picture H. sync signal input      |                              |

| 14  |               |                                |        |                                        |                              |

| 15  | AFT2 IN       |                                | In     | Sub tuner AFT S-curve input            |                              |

| 16  | AFT1          | UV MAIN S-CURVE<br>SIGNAL      | In     | Main tuner AFT S-curve signal input    |                              |

| 17  | KEY A         | LOCAL KEY INPUT                | In     | Local key detection: 0 to 5V           |                              |

| 18  | KEY B         | LOCAL KEY INPUT                | In     | Local key detection: 0 to 5V           |                              |

| 19  | SGV           | TEST SIGNAL OUT                | Out    | Test signal output In normal=L         | 0V                           |

| 20  | SGA           | TEST AUDIO OUT                 | Out    | Test audio output In normal=L          | 0V                           |

| 21  | VSS           | POWER GROUNDING                |        | 0V: Gounding voltage                   | 0V                           |

| 22  | R             | R                              | Out    |                                        | At display on:Pulse          |

| 23  | G             | G                              | Out    |                                        | At dispaly on:Pulse          |

| 24  | В             | В                              | Out    |                                        | At dispaly on:Pulse          |

| 25  | Y/BL          | BL                             | Out    |                                        | At dispaly on:Pulse          |

| 26  | HSYNC         |                                | In     | HSYNC for OSD display                  | Pulse                        |

| 27  | VSYNC         |                                | In     | VSYNC for OSD display                  | Pulse                        |

| 28  | OSC1          | DISPLAY CLOCK                  | Out    | 4.5MHz                                 | Pulse                        |

| 29  | OSC2          | DISPLAY CLOCK                  | In     |                                        | Pulse                        |

| 30  | TEST          | TEST MODE                      | In     | GND fixed                              | 0V                           |

| 31  | XIN           | SYSTEM CLOCK                   | In     | System clock input                     | 8MHz pulse                   |

| 32  | XOUT          | SYSTEM CLOCK                   | Out    | System clock output 8MHz               | 8MHz pulse                   |

| 33  | RESET         | SYSTEM RESET                   | In     | System reset input (In reset=L)        | 5V                           |

| 34  | SW IN         |                                |        |                                        |                              |

| 35  | RMT IN        | REMOTE CONTROL<br>SIGNAL INPUT | IN     | In remote control pulse input=L        | In reception of remote pulse |

| 36  | SYNC AV1      | HSYNC INPUT                    | In     | External H. sync signal input          | Pulse                        |

| 37  | SCL1          | IIC BUS CLOCK OUT              | Out    | IIC bus clock output 1                 | Pulse                        |

| 38  | SDA1          | IIC BUS DATA IN/OUT            | In/Out | IIC bus data input/output 1            | Pulse                        |

| 39  | GND           |                                |        |                                        | 0V                           |

| 40  | NC            |                                |        |                                        |                              |

| 41  | ACP           | NSYNC INPUT                    | In     | AC pulse input                         |                              |

| 42  | VDD           | POWER                          |        | 5V                                     | 5V                           |

### 5. EEPROM (QA02)

EEPROM (Non volatile memory) has function which, in spite of power-off, memorizes the such condition as channel selecting data, last memory status, user control and digital processor data. The capacity of EEPROM is 8k bits. Type name is 24LC08BI/ P or ST24C08CB6, and those are the same in pin allocation and function, and are exchangeable each other. This IC controls through I<sup>2</sup>C bus. The power supply is common to the EEPROM and the main MICOM. Pin function of EEPROM is shown in Fig. 3-3.

Fig. 3-3

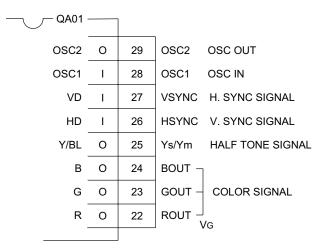

### 6. ON SCREEN FUNCTION

ON SCREEN FUNCTION indicates data like channel, volume. Formerly, exclusive use of OSD IC was used, but in N5SS, the OSD function is within the main microcomputer. Pin function concerning on-screen data generation is shown in Fig. 3-4. Oscillation clock of OSD is approx. 4.5MHz. 9MHz which becomes multiplied by two to become the dot clock i slocated within the microcomputer. For oscillation, a coil TRF1160D (LA02) is used.

Fig. 3-4

### 7. SYSTEM BLOCK DIAGRAM

Fig. 3-5

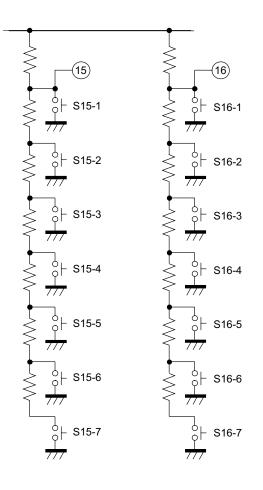

### 8. LOCAL KEY DETECTION METHOD

Local key detection in the N5SS chassis is carried out by using an analog voltage divider-like method which detects a voltage appearing at the local key input terminals (pins 17, 18) of the microcomputer whenever a key is depressed. Using this method, a maximum of 14 keys can be interpreted.

The circuit diagram shown at the left is a representation of the local key circuit. As can be seen from the diagram, when one of keys among SA-01 to SA-08 is pressed, each of two input terminals (pins 17, 18) develops a voltage (Vin) corresponding to the key pressed. (The voltage measurement and key identification are carried out by an A/D converter inside the microcomputer along with interpreting software.

Fig. 3-6. Local key assignment

| Key No. | Function       | Key No. | Function        |

|---------|----------------|---------|-----------------|

| SA-02   | POWER          | SA-01   | DEMO START/STOP |

| SA-03   | CH UP          |         |                 |

| SA-04   | CH DN          |         |                 |

| SA-05   | VOL UP         |         |                 |

| SA-06   | VOL DN         |         |                 |

| SA-07   | ANT/VIDEO, ADV |         |                 |

| SA-08   | MENU           |         |                 |

Table 3-1 Local key assinment

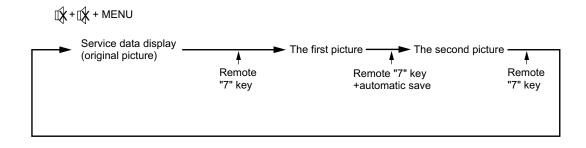

### 9. ENTERING THE SERVICE MODE

#### 1. PROCEDURE

- (1) Press once MUTE key on the remote hand unit to indicate MUTE on screen of the television.

- (2) Press the MUTE key of remote hand unit again and keep depressed while depressing the MENU key on the front of the unit.

- 2. During service mode, indication S is displayed at upper right corner on screen.

### **10. TEST SIGNAL SELECTION**

- 1. In OFF state of test signal, SGA terminal (Pin 20) and SGV terminal (Pin 21) are kept at a "L" condition.

- 2. The function of VIDEO test signal selection is cyclically changed with each depression of the VIDEO key (on the remote control unit).

| Test Signal No. | Name of Pattern                         |

|-----------------|-----------------------------------------|

| 0               | Signal OFF                              |

| 1               | All black signal + R single color (OSD) |

| 2               | All black signal + G single color (OSD) |

| 3               | All black signal + B single color (OSD) |

| 4               | All black signal                        |

| 5               | All white signal                        |

| 6               | W/B                                     |

| 7               | Black cross bar                         |

| 8               | White cross bar                         |

| 9               | Black cross hatch                       |

| 10              | White cross hatch                       |

| 11              | White cross dot                         |

| 12              | Black cross dot                         |

| 13              | H signal (bright area)                  |

| 14              | H signal (dark area)                    |

| 15              | Black cross + G                         |

#### Table 3-2

(3) SGA (audio test signal) output should be square wave of 1kHz.

### **11. SERVICE ADJUSTMENT**

- 1. ADJUSTMENT MENU INDICATION ON/OFF, MENU key ( on TV set)

- 2. During display of the adjustment menu, the following functions are possible:

- a) Selection of adjustment item : POS UP/DN key (on TV/remote unit)

- b) Adjustment of each item : VOL UP/ DN key (on TV / remote unit)

- c) Direct selection of adjustment item

| R CUTOFF | : 1 POS (remote unit)       |

|----------|-----------------------------|

| G CUTOFE | $\cdot 2 POS$ (remote unit) |

| UCUIUII         | $\cdot 2 r OS (remote unit)$ |

|-----------------|------------------------------|

| <b>B</b> CUTOFF | : 3 POS (remote unit)        |

- d) Data setting for PC unit adjustment

SUB CONTRAST : 4 POS (remote unit)

SUB COLOR : 5 POS (remote unit)

SUB TINT : 6 POS (remote unit)

- e) Horizontal line ON/OFF : VIDEO (TV) (NOTE: applies only to direct view)

- \* In service mode, serviceable items are limited.

- 3. Test audio signal ON / OFF : 8 POS (remote unit) \* Test audio signal : 1kHz

- 4. Self check display : 9 POS (remote unit) \* Cyclic display (including ON/OFF)

- 5. Initialization of memory :

- CALL (remote unit) + POS UP (TV)

- 6. Initialization of self check data :

- CALL (remote unit) + POS DN (TV)

- 7. BUS OFF :

CALL (remote unit) + VOL UP (TV)

f) Test signal selection : VIDEO (remote unit)

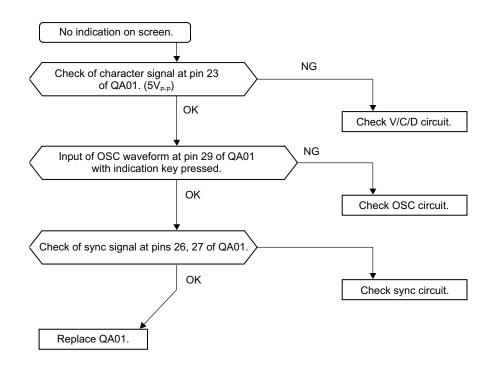

## **12. FAILURE DIAGNOSIS PROCEDURE**

The N5SS chassis is equipped with a self diagnosis function inside, used for troubleshooting.

### 1. CONTENTS TO BE CONFIRMED BY CUSTOMER BEFORE SERVICE CALL IS MADE

| Table 3-3                                                                                                                                                                                    |                                                                                                                                                                                                                                                                               |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Contents of self diagnosis                                                                                                                                                                   | Display items and actual operation                                                                                                                                                                                                                                            |  |  |  |

| <ul> <li>A. DISPLAY OF FAILURE INFORMATION<br/>IN NO PICTURE (Condition of display)</li> <li>1. When power protection circuit operates;</li> <li>2. When I2C-BUS line is shorted;</li> </ul> | <ul><li>Power indicator lamp blinks and picture does not come.</li><li>1. Power indicator red lamp blinks. (0.5 seconds interval)</li><li>2. Power indicator red lamp blinks. (1 seconds interval)</li><li>If these indication appears, repairing work is required.</li></ul> |  |  |  |

2. CONTENTS TO BE CONFIRMED BY SERVICER (Check in self diagnosis mode)

| Contents of self diagnosis                                                                                                                                                          | Display items and actual operation                                                                                                                                                              |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Contents of self diagnosis<br><countermeasure always="" arises.="" case="" in="" phenomenon="" that=""><br/>B. Detection of shortage in BUS line</countermeasure>                   | Display items and actual operation                                                                                                                                                              |  |  |  |

| C. Check of comunication status in BUS line                                                                                                                                         | (Example of screen display)                                                                                                                                                                     |  |  |  |

| <ul><li>D. Check of signal line by sync signal detection</li><li>E. Indication of part code of microcom.(QA01)</li><li>F. Number of operation of power protection circuit</li></ul> | SELF CHECK         NO. 239XXXX          ← Part coce of QA01         POWER: 000000       Number of operation of power protection circuit         BUS LINE: OK          ← Short check of bus line |  |  |  |

|                                                                                                                                                                                     | BUS CONT: OK Communication check of busline<br>BLOCK: UV V1 V2<br>QV01, QV01S                                                                                                                   |  |  |  |

#### Table 3-4

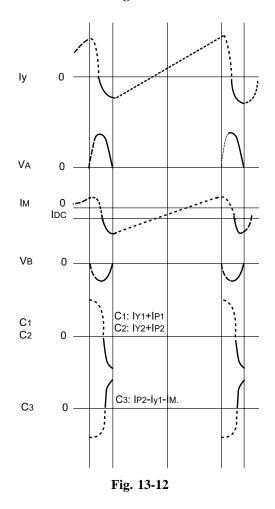

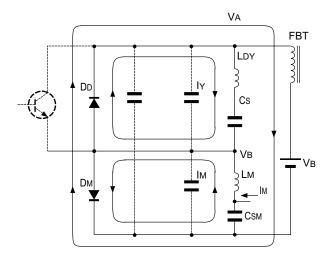

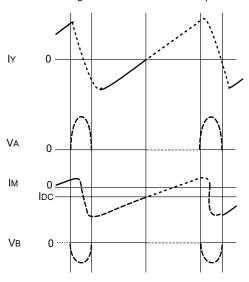

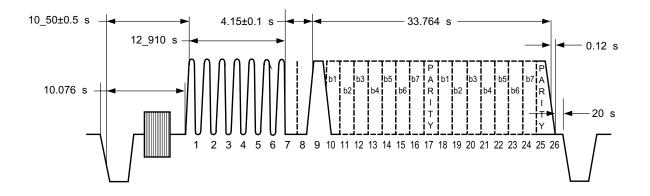

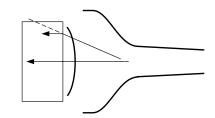

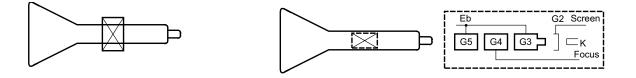

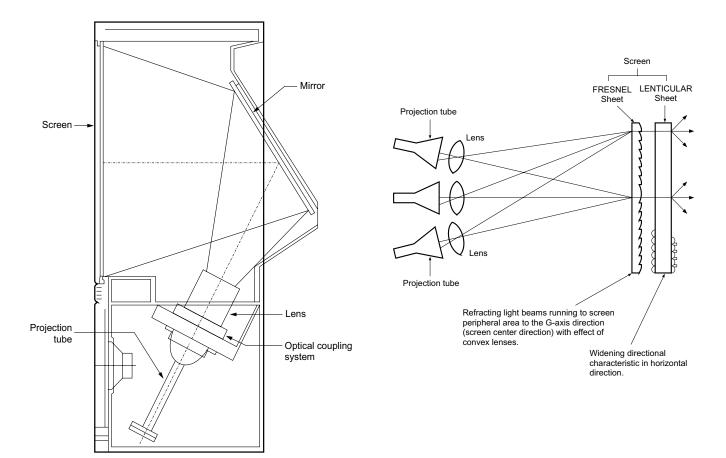

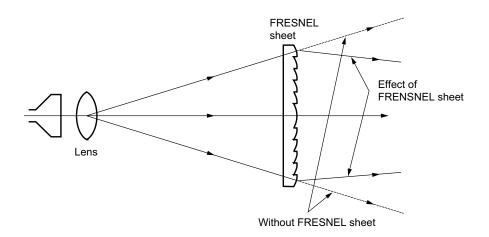

#### 3. EXECUTING SELF DIAGNOSIS FUNCTION [CAUTION]